#### **BTC Capabilities Overview**

#### IEEE 802.16 Presentation Submission Template (Rev. 8)

Document Number: IEEE 802.16.1pp-00/35 Date Submitted: 2000-7-10 Source:

| David G. Williams                     | Voice:  | 509-334-1000  |

|---------------------------------------|---------|---------------|

| Advanced Hardware Architectures, Inc. | Fax:    | 509-334-9000  |

| 2365 NE Hopkins Ct                    | E-mail: | davew@aha.com |

| Pullman, WA 99163                     |         |               |

Venue: 802.16.1 Session #8, FEC Ad Hoc review

Base Document: IEEE 802.16.1pc-00/35

#### Purpose:

This presentation summarizes the Block Turbo Code submittal to the the FEC Ad Hoc committee.

Notice:

This document has been prepared to assist IEEE 802.16. It is offered as a basis for discussion and is not binding on the contributing individual(s) or organization(s). The material in this document is subject to change in form and content after further study. The contributor(s) reserve(s) the right to add, amend or withdraw material contained herein.

Release:

The contributor grants a free, irrevocable license to the IEEE to incorporate text contained in this contribution, and any modifications thereof, in the creation of an IEEE Standards publication; to copyright in the IEEE's name any IEEE Standards publication even though it may include portions of this contribution; and at the IEEE's sole discretion to permit others to reproduce in whole or in part the resulting IEEE Standards publication. The contributor also acknowledges and accepts that this contribution may be made public by IEEE 802.16.

IEEE 802.16 Patent Policy:

The contributor is familiar with the IEEE 802.16 Patent Policy and Procedures (Version 1.0) <<u>http://ieee802.org/16/ipr/patents/policy.html</u>>, including the statement "IEEE standards may include the known use of patent(s), including patent applications, if there is technical justification in the opinion of the standards-developing committee and provided the IEEE receives assurance from the patent holder that it will license applicants under reasonable terms and conditions for the purpose of implementing the standard."

Early disclosure to the Working Group of patent information that might be relevant to the standard is essential to reduce the possibility for delays in the development process and increase the likelihood that the draft publication will be approved for publication. Please notify the Chair <<u>mailto:r.b.marks@ieee.org</u>> as early as possible, in written or electronic form, of any patents (granted or under application) that may cover technology that is under consideration by or has been approved by IEEE 802.16. The Chair will disclose this notification via the IEEE 802.16 web site <<u>http://ieee802.org/16/ipr/patents/letters></u>.

# Block Turbo Code

# (Turbo Product Code)

# Capability and Benefit Summary

David Williams Advanced Hardware Architectures

#### Davew@aha.com

7/10/00 Based on 802161pc-00\_35

### Overview

- Block Turbo Codes (BTCs) are very flexible

- Can support any data block size, resolution 1 bit

- BTCs can support a very wide range of code rates with a single, unified encoder/decoder strategy

- From below rate 1/3 to as high as rate 0.98

- Multiple vendor support exists

- Simulation results show that performance results are similar for different vendor implementations

# 802.16 Small Block Performance

| Code                                                  | 39,32 x 39,32<br>sb 0                      | 46,39 x 46,39<br>sb 17                        | 63,56 x 63,56<br>sb 0                      |

|-------------------------------------------------------|--------------------------------------------|-----------------------------------------------|--------------------------------------------|

| Aggregate Code Rate                                   | 0.673                                      | 0.717                                         | 0.790                                      |

| Uplink/Downlink/Both                                  | Downlink                                   | Downlink                                      | Downlink                                   |

| Eb/No Required @ 10 <sup>-6</sup><br>QPSK/16QAM/64QAM | 3.5/6.5/10.7 dB                            | 3.6/6.6/10.5 dB                               | 3.5/6.9/11.0 dB                            |

| Eb/No Required @ 10 <sup>-9</sup><br>QPSK/16QAM/64QAM | 4.3/7.5/11.7 dB                            | 4.3/7.8/11.5 dB                               | 4.3/7.5/12.0 dB                            |

| Encoder Complexity<br>QPSK/16QAM/64QAM                | 10 Kgates                                  | 10 Kgates                                     | 10 Kgates                                  |

| Decoder Complexity<br>QPSK/16QAM/64QAM                | < 150 Kgates @ 5 iter<br>and 240 Mbits/sec | < 150 Kgates @ 5<br>iter and 240<br>Mbits/sec | < 150 Kgates @ 5 iter<br>and 240 Mbits/sec |

| Block size (payload bits)                             | 1024 (128 bytes)                           | 1504 (188 bytes)                              | 3136 (392 bytes)                           |

| Latency                                               | < 2 coded blocks                           | < 2 coded blocks                              | < 2 coded blocks                           |

Note: Gate counts are for a single encoder or decoder that supports all of the small block codes shown. Estimates take into account all memory requirements.

- 5, 14 and 57 byte codes also included in submittal

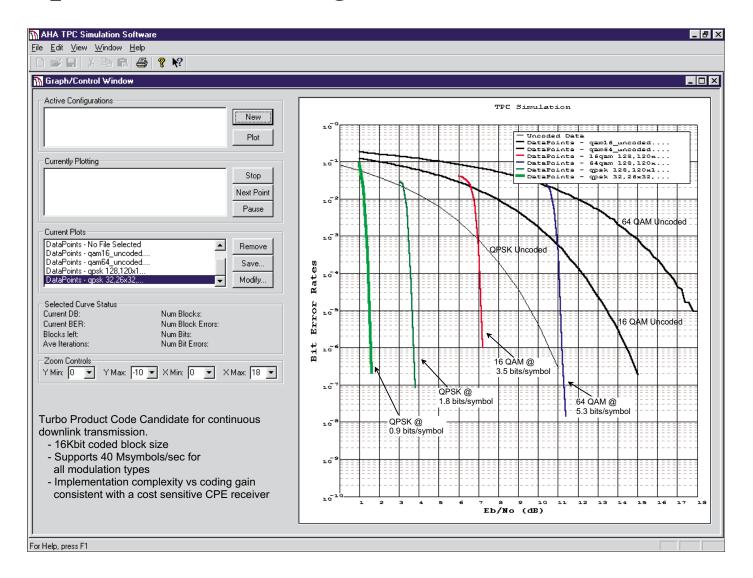

## Large Block Code Performance

- Large Block can provide significant code rate and coding gain advantages

- Code rates as high as R = 0.98 for higher bandwidth efficiency

- Optimal efficiency for continuous downstream transmission

- A single unified decoder design will also support the small block codes but with higher coding gain when the larger blocks are used

- Enhanced burst error performance without interleaving

# Large Block Performance

| Code                                   | 32,26 x 32,26 x<br>16,11 (sb 4) | 128,120 x<br>128,120<br>(sb 0) | 128,127 x 128,127<br>(sb 1) |

|----------------------------------------|---------------------------------|--------------------------------|-----------------------------|

| Aggregate Code Rate                    | 0.454                           | 0.880                          | 0.980                       |

| Uplink/Downlink/Both                   | Downlink                        | Downlink                       | Downlink                    |

| Eb/No Required @ 10 <sup>-6</sup>      | 1.5 dB                          | 3.8 dB                         | 7.5 dB                      |

| Eb/No Required @ 10 <sup>-9</sup>      | 1.8 dB                          | 4.0 dB                         | 8.5 dB                      |

| Encoder Complexity<br>QPSK/16QAM/64QAM | 15 Kgates                       | 15Kgates                       | 15 Kgates                   |

| Decoder Complexity<br>QPSK/16QAM/64QAM | < 250 Kgates                    | < 250 Kgates                   | < 250 Kgates                |

| Block size (payload bits)              | 7,432                           | 14,400                         | 16,128                      |

| Latency                                | 2 blocks max                    | 2 blocks max                   | 2 blocks max                |

Notes: The complexity estimates are provided for data rate of 240 Mbit/s. For data rates of up to 150 Mbit/s the complexity will be reduced significantly. Gate counts are estimates which include required RAM (2 bits = 1 gate equiv), 5 iterations and 4 soft input bits to decoder. Dropping iterations to 4 iterations will reduce performance by about 0.1 dB but will also reduce complexity significantly.

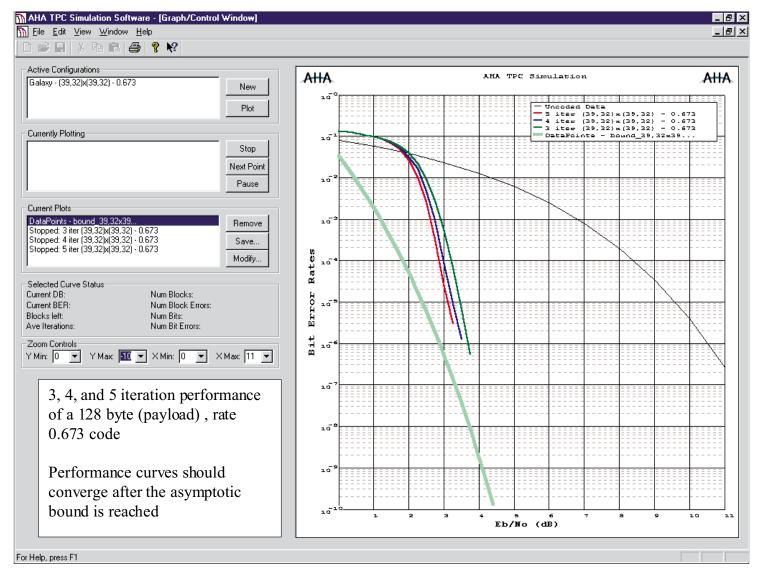

## Effect of Decoder Iterations on Performance

#### Representative Large Block Performance

### Availability and Time to Market

- BTC hardware is available and fielded for almost 2 years

- Two different BTC evaluation systems are available

- A single chip encoder/decoder that supports channel rates up to 300 Mbits/sec will be available in Q3CY00

- Supports both small and large block codes

- Full duplex encoder and decoder

- Supports QPSK, 16 QAM and 64 QAM needed for 802.16

- BTC cores available for ASIC integration

- VHDL or Verilog targeted to any foundry

- Simulation tools available

- Includes high order modulation support

- Includes C/C++ and/or Matlab support

- Facilitates system level simulations for channel models, phase jitter, burst noise and other impairments

### Conclusions

- All coding schemes proposed including traditional RSV and RS+BC provide good performance

- BTCs provide best performance and can offer a very wide range of block sizes and code rates with no change in coding strategy

- BTC codes have multiple vendor availability

- Both off the shelf ICs and ASIC Cores are available