| Project                            | IEEE 802.16 Broadband Wireless <a href="http://ieee802.org/16">http://ieee802.org/16&gt;</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Access Working Group                                                                                        |  |  |

|------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|--|--|

| Title                              | MSS's buffer capability negotiation for DL H-ARQ operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                             |  |  |

| Date<br>Submitted                  | 2004-11-02                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                             |  |  |

| Source(s)                          | kang-gyuLee, yunsungKim, sajinKim, jae-hwanChang, yunsangPark, Jaehee Cho, Geunhwi Lim,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | leekg@samsung.com tseliot@samsung.com sj.kim@samsung.com jaehwan.chang@samsung.com yunsang.park@samsung.com |  |  |

| Re:                                | This contribution is for call for contribution about IEEE P802.16e/D5-2004                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                             |  |  |

| Abstract                           | This contribution proposes the MSS buffer capability information for H-ARQ.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                             |  |  |

| Purpose                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                             |  |  |

| Notice                             | This document has been prepared to assist IEEE 802.16. It is offered as a basis for discussion and is not binding on the contributing individual(s) or organization(s). The material in this document is subject to change in form and content after further study. The contributor(s) reserve(s) the right to add, amend or withdraw material contained herein.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                             |  |  |

| Release                            | The contributor grants a free, irrevocable license to the IEEE to incorporate material contained in this contribution, and any modifications thereof, in the creation of an IEEE Standards publication; to copyright in the IEEE's name any IEEE Standards publication even though it may include portions of this contribution; and at the IEEE's sole discretion to permit others to reproduce in whole or in part the resulting IEEE Standards publication. The contributor also acknowledges and accepts that this contribution may be made public by IEEE 802.16.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                             |  |  |

| Patent<br>Policy and<br>Procedures | The contributor is familiar with the IEEE 802.16 Patent Policy and Procedures <a href="http://ieee802.org/16/ipr/patents/policy.html">http://ieee802.org/16/ipr/patents/policy.html</a> , including the statement "IEEE standards may include the known use of patent(s), including patent applications, provided the IEEE receives assurance from the patent holder or applicant with respect to patents essential for compliance with both mandatory and optional portions of the standard." Early disclosure to the Working Group of patent information that might be relevant to the standard is essential to reduce the possibility for delays in the development process and increase the likelihood that the draft publication will be approved for publication. Please notify the Chair <a href="mailto:chair@wirelessman.org">mailto:chair@wirelessman.org</a> as early as possible, in written or electronic form, if patented technology (or technology under patent application) might be incorporated into a draft standard being developed within the IEEE 802.16 Working Group. The Chair will disclose this notification via the IEEE 802.16 web site <a href="http://ieee802.org/16/ipr/patents/notices">http://ieee802.org/16/ipr/patents/notices</a> . |                                                                                                             |  |  |

# MSS's HARQ buffer capability negotiation for DL H-ARQ operation

Kang-gyu Lee, jae-hwan Chang, sajin Kim, yunsung Kim, yunsang Park

## SAMSUNG ELECTRONICS

## 1. Problem statements

H-ARQ scheme is an optional and can be enabled on per-terminal basis. This scheme may be supported only for the OFDMA PHY. The signaling of the per-terminal H-ARQ and associated parameters shall be done during initialization procedure. The associated parameters mentioned above are (M)SS Capability encodings, bandwidth allocation support, capabilities for construction and transmission of MAC PDUs and physical parameters supported and many others. For the IR H-ARQ scheme, the MSS shall be able to store the different versions of subpackets to successfully decode the corresponding H-ARQ encoded packet. The MSS shall be capable of supporting the reordering to deliver the received MAC PDUs to the upper layer in order.

If the BS knows the MSS memory ability, the BS may allocate the reasonable amount of downlink H-ARQ resource to the MSS through compact DL-MAP IE. If the BS allocates the downlink H-ARQ bandwidth to the MSS without the MSS buffer ability, the MSS may fail to decode the downlink H-ARQ encoded packet because of lack of memory. The more H-ARQ channels, the more storages the MSS needs.

Without signaling of MSS buffer capability, even though the channel condition is getting enough good, the possibility of retransmission and the traffic latency may be increased because of MSS buffer overflow. Therefore, it needs MSS buffer capability signaling during initialization procedure.

## 2. Proposed remedy

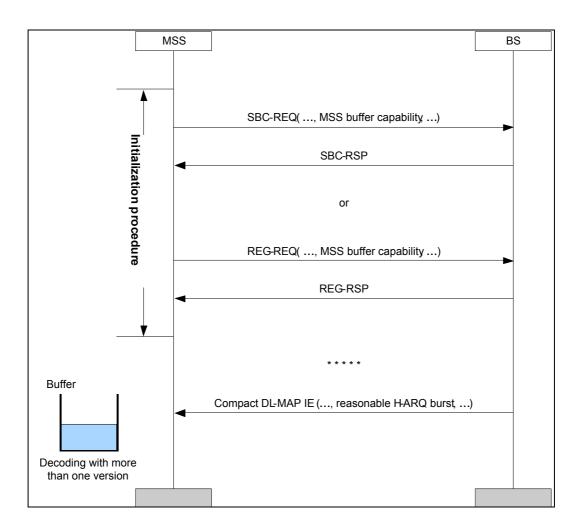

Add the parameter 'MSS buffer capability' into (M)SS Capability encodings which may be included in SBC-REQ/SBC-RSP or REG-REQ/REG-RSP messages. The H-ARQ enabled MSS informs the BS of its buffer capability during initialization procedure as follows.

Figure 1. H-ARQ procedure with MAC buffer capability signaling

## 3. Proposed text change

#### [Change section 6.3.17 as indicated]

Hybrid automatic repeat request (H-ARQ) scheme is an optional part of the MAC and can be enabled on a per-terminal basis. H-ARQ may be supported only for the OFDMA PHY. The per-terminal H-ARQ and associated parameters shall be specified and negotiated during initialization procedure. A burst can not have a mixture of H-ARQ and non-H-ARQ traffic.

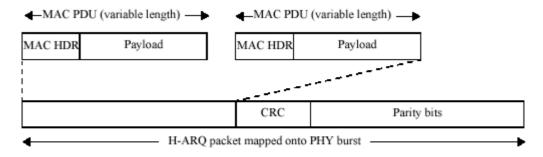

One or more MAC PDUs can be concatenated and an H-ARQ packet formed by adding a CRC to the PHY burst. Figure 130 shows how the H-ARQ encoder packet is constructed.

Figure 130—Construction of H-ARQ encoder packet

Two main variants of H-ARQ are supported, Chase Combining or Incremental Redundancy (IR). For IR, the PHY layer will encode the H-ARQ packet generating several versions of encoded subpackets. Each subpacket shall be uniquely identified using a subpacket identifier (SPID). For Chase Combining, the PHY layer shall encode the H-ARQ packet generating only one version of the encoded packet. As a result, no SPID is required for Chase Combining.

For downlink H-ARQ operation, the BS will send a version of the encoded H-ARQ packet. The MSS will attempt to decode the encoded packet on this first H-ARQ attempt. If the decoding succeeds, the MSS will send an ACK to the BS. If the decoding fails, the MSS will send a NAK to the BS. In response, the BS will send another H-ARQ attempt. The BS may continue to send H-ARQ attempts until the MSS successfully decodes the packet and sends an acknowledgement.

For IR, each H-ARQ attempt may have a uniquely encoded subpacket. The rule of subpacket transmission is as follows:

- 1) At the first transmission, BS shall send the subpacket labeled '00'.

- 2) BS may send one among subpackets labeled '00', '01', '10', or '11' in any order.

- 3) BS can send more than one copy of any subpacket, and can omit any subpacket except the subpacket labeled '00'.

In order to specify the start of a new transmission, one-bit H-ARQ identifier sequence number (AI\_SN) is toggled on every H-ARQ attempt on the same H-ARQ channel. If the AI\_SN changes, the receiver treats the corresponding H-ARQ attempt as belonging to a new encoder packet, and discards previous H-ARQ attempt with the same ARQ identifier.

The H-ARQ scheme is basically a stop-and-wait protocol. The ACK is sent by the MSS after a fixed delay (synchronous ACK) defined by H-ARQ DL ACK delay offset which is specified in DCD message. Timing of retransmission is, however, flexible and corresponds to the asynchronous part of the H-ARQ. The ACK/NAK is sent by the BS using the H-ARQ Bitmap IE, and sent by a MSS using the fast feedback UL subchannel.

The H-ARQ scheme supports multiple H-ARQ channels per a connection, each of which may have an encoder packet transaction pending. The number of H-ARQ channels in use is determined by BS. These ARQ channels are distinguished by an H-ARQ channel identifier (ACID). The ACID for any subpackets can be uniquely identified by the control information carried in the MAPs.

H-ARQ can be used to mitigate the effect of channel and interference fluctuation. H-ARQ renders performance improvement due to SNR gain and time diversity achieved by combining previously erroneously decoded packet and retransmitted packet. The MSS which supports H-ARQ scheme shall be equiped with enough buffer ability to perform the combining of several versions of H-ARQ encoded packets and reordering of the successfully decoded H-ARQ

packets. Therefore, MSS buffer capability associated with H-ARQ shall be specified and negotiated duing initialization procedure.

[Add the following text to section 11.7.8] 11.7.8.11 HARQ buffer capability

This parameter defines the MSS ability to process the received H-ARQ packets. For IR, the MSS shall have enough memory to store more than one H-ARQ encoded packet and support reordering of the received H-ARQ packets. During the initialization procedure, the MSS needs to inform the BS of its ability for DL-HARQ. After establishment of H-ARQ service connection, the BS shall allocate the downlink resource for the established H-ARQ service based on the signaled MSS buffer ability.

| Type | Length | Value                                               | Scope   |

|------|--------|-----------------------------------------------------|---------|

| 22   | 1      | Index that defines the MSS buffer capability for DL | REG-REQ |

|      |        | HARQ connections.                                   | REG-RSP |

|      |        |                                                     | SBC-REQ |

|      |        |                                                     | SBC-RSP |

The following table defines the indices above mentioned.

Table 1 xxx- Index for HARQ buffer capability

| Index   | Buffer capability                          | Default N <sub>EP</sub> (Index/16)    | Number of H-ARQ channels (N) |

|---------|--------------------------------------------|---------------------------------------|------------------------------|

| 0 15    | An index means that the MSS has enough     | 144                                   | 1 16                         |

|         | buffer to properly process ((Index%16)+1)  | (Index/16=0)                          |                              |

|         | H-ARQ channels with $N_{EP} = 144$ bits.   |                                       |                              |

| 16 31   | An index means that the MSS has enough     | 192                                   | 1 16                         |

|         | buffer to properly process ((Index%16)+1)  | (Index/16=1)                          |                              |

|         | H-ARQ channels with $N_{EP} = 192$ bits.   | , , , , , , , , , , , , , , , , , , , |                              |

| 32 47   | An index means that the MSS has enough     | 288                                   | 1 16                         |

|         | buffer to properly process ((Index%16)+1)  | (Index/16=2)                          |                              |

|         | H-ARQ channels with $N_{EP} = 288$ bits.   | , , , , , , , , , , , , , , , , , , , |                              |

| 48 63   | An index means that the MSS has enough     | 384                                   | 1 16                         |

|         | buffer to properly process ((Index%16)+1)  | (Index/16=3)                          |                              |

|         | H-ARQ channels with $N_{EP} = 384$ bits.   | , , , , , , , , , , , , , , , , , , , |                              |

| 64 79   | An index means that the MSS has enough     | 480                                   | 1 16                         |

|         | buffer to properly process ((Index%16)+1)  | (Index/16=4)                          |                              |

|         | H-ARQ channels with $N_{EP} = 480$ bits.   |                                       |                              |

| 80 95   | An index means that the MSS has enough     | 960                                   | 1 16                         |

|         | buffer to properly process ((Index%16)+1)  | (Index/16=5)                          |                              |

|         | H-ARQ channels with $N_{EP} = 960$ bits.   |                                       |                              |

| 96 111  | An index means that the MSS has enough     | 1920                                  | 1 16                         |

|         | buffer to properly process ((Index%16)+1)  | (Index/16=6)                          |                              |

|         | H-ARQ channels with $N_{EP} = 1920$ bits.  |                                       |                              |

| 112 127 | An index means that the MSS has enough     | 2880                                  | 1 16                         |

|         | buffer to properly process ((Index%16)+1)  | (Index/16=7)                          |                              |

|         | H-ARQ channels with $N_{EP} = 2880$ bits.  |                                       |                              |

| 128 143 | An index means that the MSS has enough     | 3840                                  | 1 16                         |

|         | buffer to properly process ((Index%16)+1)  | (Index/16=8)                          |                              |

|         | H-ARQ channels with $N_{EP} = 3840$ bits.  |                                       |                              |

| 144 159 | An index means that the MSS has enough     | 4800                                  | 1 16                         |

|         | buffer to properly process ((Index%16)+1)  | (Index/16=9)                          |                              |

|         | H-ARQ channels with $N_{EP} = 4800$ bits.  |                                       |                              |

| 160 175 | An index means that the MSS has enough     | 9600                                  | 1 16                         |

|         | buffer to properly process ((Index%16)+1)  | (Index/16=10)                         |                              |

|         | H-ARQ channels with $N_{EP} = 9600$ bits.  |                                       |                              |

| 176 191 | An index means that the MSS has enough     | 14400                                 | 1 16                         |

|         | buffer to properly process ((Index%16)+1)  | (Index/16=11)                         |                              |

|         | H-ARQ channels with $N_{EP} = 14400$ bits. |                                       |                              |

| 192 207 | An index means that the MSS has enough     | 19200                                 | 1 16                         |

|         | buffer to properly process ((Index%16)+1)  | (Index/16=12)                         |                              |

|         | H-ARQ channels with $N_{EP} = 19200$ bits. |                                       |                              |

| 208 223 | An index means that the MSS has enough     | 24000         | 1 16 |

|---------|--------------------------------------------|---------------|------|

|         | buffer to properly process ((Index%16)+1)  | (Index/16=13) |      |

|         | H-ARQ channels with $N_{EP} = 24000$ bits. |               |      |

According to table xxx, the default  $N_{EP}$  size for index/16=0 is 144, 1 is 192, and so forth. Finally, default  $N_{EP}$  size for index/16=13 is 24000. The BS shall not allocate more bits than the (default  $N_{EP}$  size that corresponds to the signaled index) \* ((Index%16)+1) as the downlink HARQ burst for the MSS. The BS may also assign the downlink HARQ burst to the MSS which has informed its HARQ buffer capability index i, i=0...223, as follows.

If  $M * S \le (\text{default size corresponds to } i)*((i\%16) +1)$ , BS may allocate M HARQ channels to the MSS and transmit  $N_{EP} = S$  bits on each HARQ channel.

Here, M means the number of HARQ channel(s) which the BS may actually allocate to the MSS.

S means the actual  $N_{EP}$  size that the BS allocates to the MSS and may not same as the default size for the index the MSS informed to the BS.