Worst-Case Analysis of PoE System Efficiency

**Steve Robbins**

#### Overview

- One of the biggest costs in a PSE is the cost of the main power supply.

- Presently, the main PS is oversized in many systems because a lot of power is wasted in various ways.

- If waste could be reduced, we may be able to significantly reduce the size of the main PS, and thus the cost of a PSE system.

- This document seeks to:

- $\Box$  Analyze the various ways that power is wasted.

- □ Suggest ways to reduce these waste factors.

- Estimate the resulting PSE system cost savings.

#### What is "Wasted Power"?

- Normally in power electronics we talk about efficiency and losses.

- The term "loss" traditionally refers to energy that is converted to heat. To avoid confusion, we'll stick with that definition.

- But in PoE systems, losses are only part of the inefficiency: Most of the waste is caused by margining, and protocol limitations.

- Definition: Wasted power, is power within the capacity of the PSE to provide, but it can't actually be used by the PDs for some reason.

## Where Does All the Power Go?

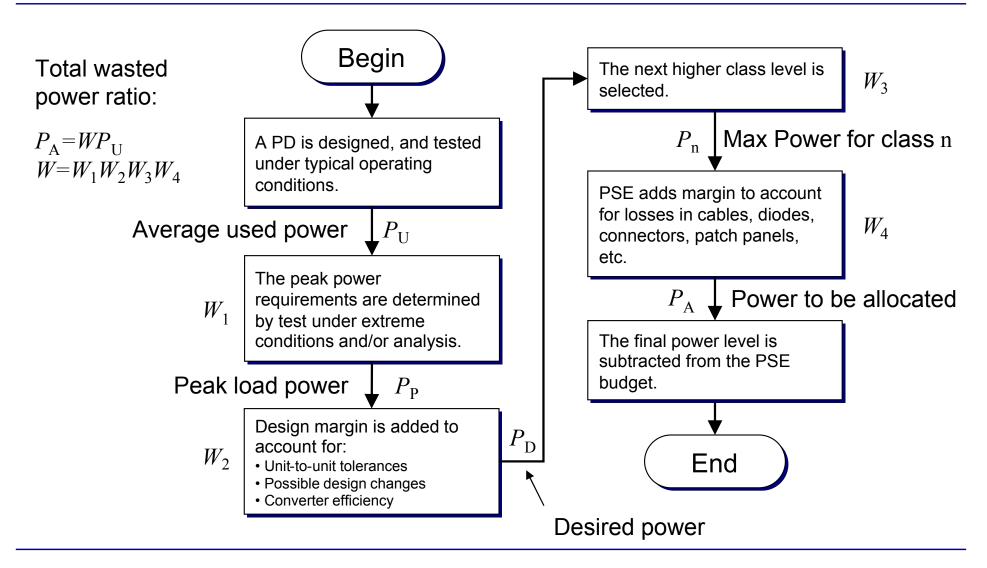

- First, let's define "wasted power ratio", denoted as W.

- □ The ratio of power <u>allocated</u> from PSE budget ( $P_A$ ), to power actually <u>used</u> by PD ( $P_U$ ).

- $\square$  W=P<sub>A</sub>/P<sub>U</sub> (Note: W is the reciprocal of Power Utilization.)

- □ For the purpose of this analysis,  $P_{\rm U}$  is the average power output from the converter inside the PD under typical operating conditions.

- Power is wasted in four ways  $(W = W_1 W_2 W_3 W_4)$ :

- $\square$   $W_1$ : Requesting peak power rather than average.

- $\square$   $W_2$ : Adding PD design margin.

- $\square$   $W_3$ : Waste due to finite classification granularity.

- $\square$   $W_4$ : Margin for losses in components (including cables).

- Each of these terms is explained in detail later.

## Modeling The Waste Process

## Some Key Points

- The expression for W is the <u>product</u> of 4 factors, not the <u>sum</u> of 4 terms.

- □ We may not know how big  $W_1$  is, but we do know that a 10% reduction in either  $W_3$  or  $W_4$  will result in a 10% reduction of W.

- □ We don't need to know  $W_1$  or  $W_2$ . It is possible to reduce the cost of PSE by working with just  $W_3$  and  $W_4$ .

- All 4 factors are examined here for the sake of completeness, but the emphasis is on  $W_3$  and  $W_4$ .

## $W_1$ : Peak vs. Average Power

- This is definitely the biggest waste of power, and the most difficult to prevent or even predict.

- Example: A PD uses 2W on average ( $P_U$ =2), but can draw up to 10W during occasional peaks ( $P_P$ =10). Then  $W_1$ =5.

- Possible ways to reduce  $W_1$ : None for L1.

- We can't change the protocol to use average instead of peak power.

- Not backward-compatible with 802.3af

- Could lead to over-committing of the main PS.

- The issue is best handled with a Layer 2 protocol, which would allow dynamic negotiation and reallocation. (Outside the scope of this presentation.)

## W<sub>2</sub>: PD Design Margin

- This is probably the second largest waste of power.

- Example: You design a PD and your prototype draws 10W at peak load. (P<sub>P</sub>=10W.) But you shouldn't request only 10W, you need some margin:

- □ There will be unit-to-unit variations.

- Converter efficiency must be considered.

- There may be new features, field upgrades, or bug fixes that increase peak power.

- □ You decide to set  $P_D$ =12.5W (for 25% margin). Then  $W_2$ =1.25.

- Possible ways to reduce  $W_2$ :

- If the PD controller chips encoded the class signature in EEPROM instead of fixed resistors, then PD designers would probably be comfortable with smaller margins.

- Could the task force establish guidelines or recommendations for minimum converter efficiency?

# *W*<sub>3</sub>: Classification Granularity

- This was a huge waste of power for 802.3af, but will (hopefully) be much less in 802.3at.

- Example:

- □ Suppose a Af-PD requires 6.5W peak.

- □ This falls within the range of Class 3. (Table 33-10)

- □ The PSE must allocate 15.4W for a Class 3 PD. (Table 33-3)

$$\square W_3 W_4 = P_A / P_D = 15.4 / 6.5 = 2.37.$$

- □ Assume  $W_4$ =1.15 in this case (see page 17).

- □ Then  $W_3 = 2.37/1.15 = 2.06$

- Therefore 51% of the allocated power is wasted due to class granularity alone.

- Possible ways to reduce  $W_3$ :

- □ Increase class granularity.

- □ Use an exponential curve (see page 11).

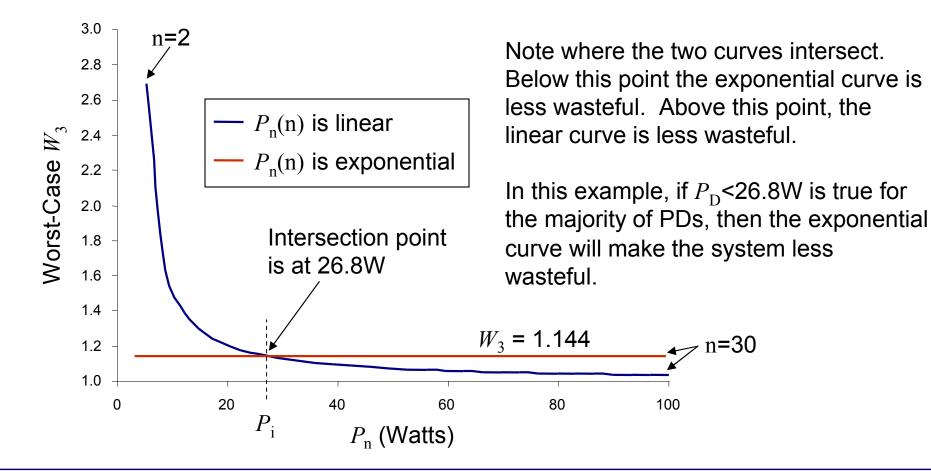

### *W*<sub>3</sub>: Worst-Case Analysis

- $W_3 = P_n/P_D$  where  $P_n$  is the upper end of the power range of class n. The worst-case is when  $P_D = P_{n-1}$ . Therefore we use  $W_3 = P_n/P_{n-1}$ . Let N be the number of classes, and  $n = \{1,..,N\}$ .

- The function P<sub>n</sub>(n) has a great impact on the analysis.

If we choose a <u>linear</u> curve then,

$$P_{n} = \frac{(n-1)P_{MAX} + (N-n)P_{MIN}}{(N-1)} \implies W_{3}(n) = \frac{(n-1)P_{MAX} + (N-n)P_{MIN}}{(n-2)P_{MAX} + (N-n+1)P_{MIN}}$$

□ If we choose a <u>exponential</u> curve then,

$$P_{\rm n} = P_{\rm MIN} \left(\frac{P_{\rm MAX}}{P_{\rm MIN}}\right)^{(\rm n-1)/(\rm N-1)} \implies W_3 = \left(\frac{P_{\rm MAX}}{P_{\rm MIN}}\right)^{1/(\rm N-1)}$$

□ Both curves have end-points  $\{1, P_{MIN}\}$  and  $\{N, P_{MAX}\}$ .

#### *W*<sub>3</sub>: Comparison of Curves

• Example: Let N=30,  $P_{\text{MIN}}$ =2W, and  $P_{\text{MAX}}$ =100W.

## W<sub>3</sub>: Cost Analysis

#### Definition of variables

- $\Box$  C<sub>SYS</sub>=Total cost of manufacturing a Af-PSE (including test).

- $\Box$  *C*<sub>TEST</sub>=Cost of testing a Af-PSE (PoE and non-PoE tests).

- $\Box$   $C_{\rm PS}$ =Cost of main power supply inside PSE.

- $\square$  N<sub>TEST</sub>=Total number of test cases presently performed for Af-PSE.

- N<sub>CLASS</sub>=Number of test cases needed to verify functionality associated with all Af class signatures. (Classes 0, 1, 2, and 3.)

- Cost models (in terms of % of total system cost)

- □ Added cost of additional testing resulting from N class signatures.

$$\Delta C_{TEST} = \left(\frac{C_{TEST}}{C_{SYS}}\right) \left(\frac{N_{CLASS}}{N_{TEST}}\right) \left(\frac{N}{4} - 1\right)$$

$\Box$  Cost savings from reducing main PS size, enabled by smaller  $W_3$ .

$$\Delta C_{PS} = \left(\frac{C_{PS}}{C_{SYS}}\right) \left(1 - \frac{W_3}{2.06}\right)$$

Note: 2.06 is the worst-case  $W_3$  for Af-PSE Class 3 (See page 9).

# $W_3$ : Cost Analysis (Continued)

Assumptions:  $P_{\text{MAX}}$ =100W,  $P_{\text{MIN}}$ =2W, curve is exponential. Savings=  $\Delta C_{\text{PS}} - \Delta C_{\text{TEST}}$  N<sub>OPT</sub>=Optimal number of classes  $\left(\frac{N_{CLASS}}{N_{TEST}}\right) = 5\%$

| N <sub>OPT</sub> /Savings         |     | C <sub>TEST</sub> /C <sub>SYS</sub> |          |          |          |

|-----------------------------------|-----|-------------------------------------|----------|----------|----------|

|                                   |     | 5%                                  | 10%      | 15%      | 20%      |

| C <sub>PS</sub> /C <sub>SYS</sub> | 60% | 47/25.6%                            | 33/23.5% | 28/21.8% | 24/20.5% |

|                                   | 50% | 42/20.9%                            | 31/19.0% | 25/17.5% | 22/16.3% |

|                                   | 40% | 37/16.3%                            | 28/14.6% | 23/13.2% | 20/12.1% |

|                                   | 30% | 33/11.7%                            | 24/10.2% | 20/9.1%  | 18/8.2%  |

Example:  $C_{PS}/C_{SYS}$ =50%,  $C_{TEST}/C_{SYS}$ =10%  $\Rightarrow$  N<sub>OPT</sub>=31, Savings=19%

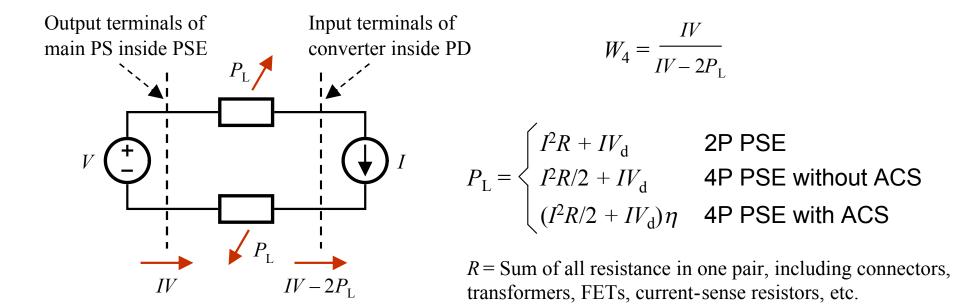

#### W<sub>4</sub>: Passive Losses

- This will probably be the third largest waste of power (assuming class granularity is improved over 802.3af).

- Define "passive" losses to include:

- Resistive losses in cables, connectors, patch panels, FETs, current-sense resistors, transformers, etc.

- □ Diode drops.

- If Active Current Sharing (ACS) is adopted, there will be some additional losses in 4P systems. (See next slide.) But this might be unavoidable to achieve the highest power.

- Possible ways to reduce  $W_4$ :

- $\Box$  Use 4P power feeding.

- If the PSE can sense that 4 pairs are present and going to the same PD, then it can reduce the margin.

- Provide a good worst-case analysis so that we don't overestimate these losses, and take too much margin.

## W<sub>4</sub>: Passive Losses (continued)

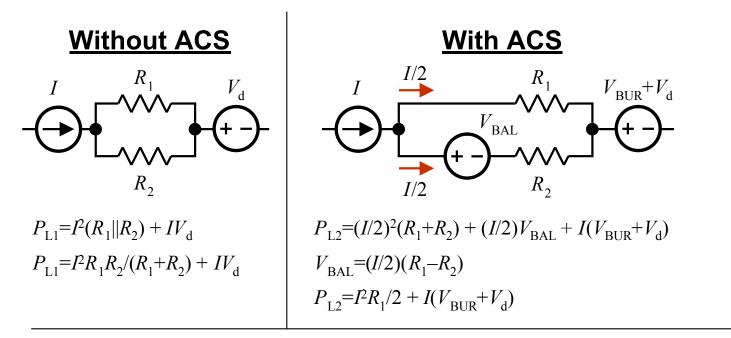

How would ACS affect the "passive" losses in 4P?

$R_1$ ,  $R_2$ = Resistance of one pair, including connectors, transformers, etc.

$V_{\rm d}$  = Total diode drops in one side of the circuit.

$V_{\rm BAL}$  = Differential voltage impressed by ACS circuit to balance the currents.

$V_{\rm BUR}$  = Common-mode burden associated with nonideal ACS circuit.

Let's define a ratio representing the extra losses associated with ACS:

$$\eta = \frac{P_{L2}}{P_{L1}}$$

Let  $R_1 = R + \Delta R/2$ ,  $R_2 = R - \Delta R/2$ . Assume  $R \gg \Delta R$  so  $R_1 R_2 \approx R^2$ . Then,

$$\eta \approx \frac{I(R + \Delta R/2) + 2(V_{\rm BUR} + V_{\rm d})}{IR + 2V_{\rm d}}$$

## W<sub>4</sub>: Passive Losses (continued)

*Note*: These equations are looking at one PSE port and one PD. Any resistance term that is common to multiple PSE ports (for example, PS output resistance) must be treated separately. This issue was neglected here for simplicity.

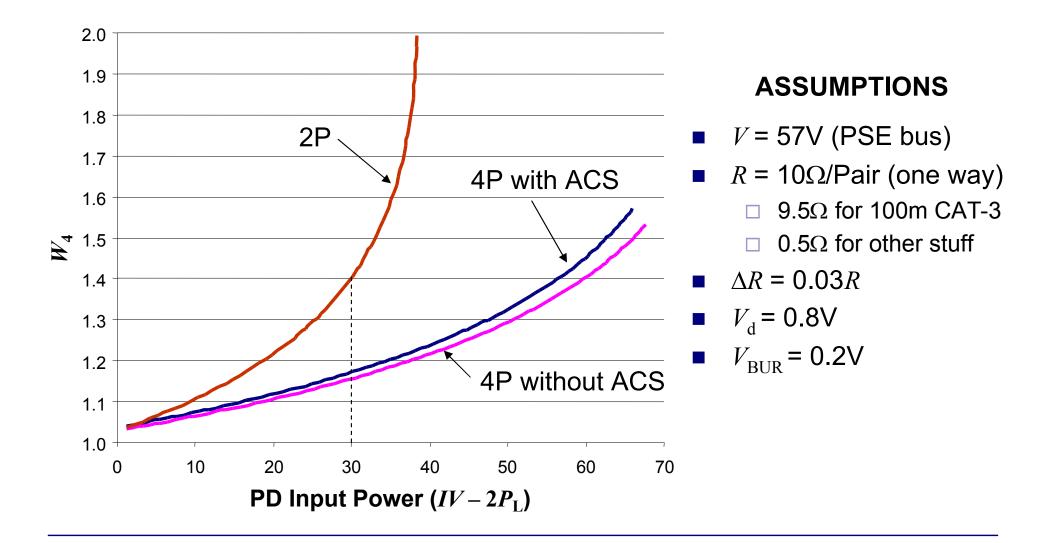

#### W<sub>4</sub>: Waste Estimates

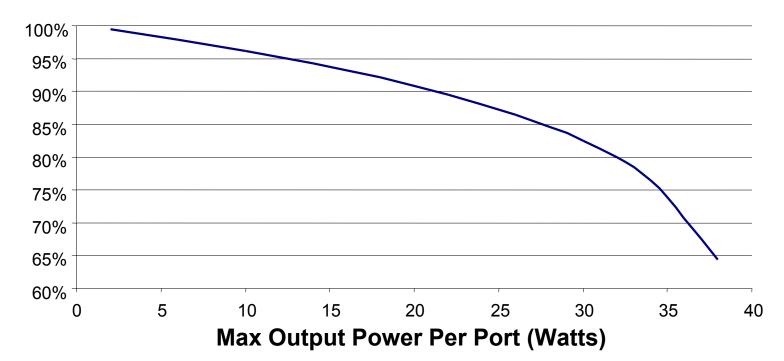

## W<sub>4</sub>: 2P vs. 4P Cost Analysis

- Required size of Main PS for 4P (without ACS) as a percent of size required for 2P.

- □ Example: For 35W/port the PS can be 26% smaller for 4P vs. 2P.

NOTE: This is just the cost reduction of the main PS, and does not take into account the other costs associated with 4P such as extra FETs, etc.

#### Conclusions

- Since the cost of the main power supply is a large portion of the overall PSE system cost, reducing wasted power can potentially result in a significant cost reduction.

- Increasing the granularity of classification may result in approx 10% to 20% cost savings.

- The optimal power curve seems to be exponential up to approx 27W, and linear for higher power.

- Using 4P instead of 2P may reduce the cost of the main power supply by another approx 25%.

- More economic analysis should be done.