# PoE Plus IEEE 802.3at Classification Ad Hoc

# Resolving Draft 1.0 Comments in L1 Bucket

Clay Stanford Linear Technology January 21, 2008 Portland

see 256

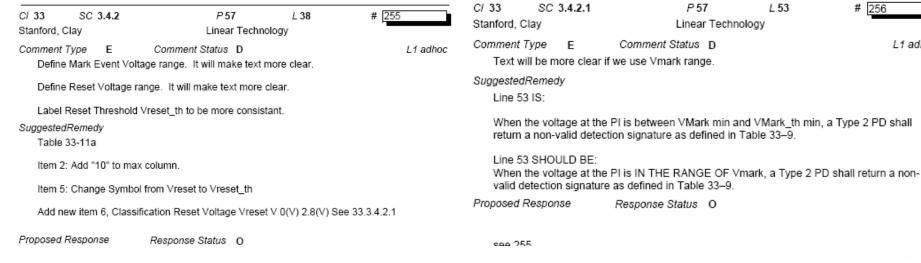

Table 33–11a—2-Event Physical Layer classification electrical requirements

10V

L1 adhoc

Ad hoc group accepts comments 255 and 256 without opposition, however see comment below.

| Item | Parameter                      | Symbol                  | Units | Min  | Max  | Additional<br>Information |

|------|--------------------------------|-------------------------|-------|------|------|---------------------------|

| 1    | Class Event Voltage            | V <sub>Class</sub>      | V     | 14.5 | 20.5 |                           |

| 2    | Mark Event Voltage             | $V_{\mathrm{Mark}}$     | V     | 6.9  |      |                           |

| 3    | Mark Event Current             | $I_{\mathrm{Mark}}$     | mA    | 0.25 | 2    | See 33.3.4.2.1            |

| 4    | Mark Event Threshold           | $V_{\mathrm{Mark\_th}}$ | v     | 10   | 14.5 | See 33.3.4.2.1            |

| 5    | Classification Reset Threshold | $V_{Reset}$             | v     | 2.8  | 6.9  | See 33.3.4.2.2            |

Vreset th

6 | Classification Reset Voltage | Vreset | V | 0 | 2.8 | See 33.3.4.2.1

Add this new entry

It was commented that standard needs margin between PSE and PD voltage ranges by making PSE <= while PD is just <. This desire is covered in PD state machine where state transitions occur when Vport<mark\_th, for example.

C/ 33 SC 2.7.2a P38 / 40 Darshan, Yair Microsemi Corporation Comment Type TR Comment Status D L1 adhoc Draft 1.0: If after Iclass Iim event the PSE classify the PD as class 4, why we need to be in Reset It looks that the text "Subsequent to such classification, the PSE shall ensure that the voltage at the PI enters the VReset range for at least TReset min as defined in Table 33-4a prior to powering the port." is not required. SuggestedRemedy Option a: Classification ad hoc to explain why we need it. If we don't need it, to delete it, Option b: Change the text to read: "If PSE decides not to complete two event classification due to any reason, or decides to ignor classification results, the PSE shall ensure that the voltage at the PI enters the VReset range for at least TReset min as defined in Table 33-4a prior to powering the port." Proposed Response Response Status O

←Accept in principle OBE See 149

C/ 33 SC 2.7.2a P 38 L 35 Schindler, Fred Cisco Systems Comment Type Comment Status D L1 adhoc The text: "... transition to the POWER ON state without allowing the voltage at the PI to go below Vmark." Conflicts with text at L40: "... shall ensure the PI enters the Vreset range..." because Vmark > Vreset. SuggestedRemedy Have the L1 ad hoc provide text to correct this section. Proposed Response Response Status O defer to L1

If any measured IClass is equal to or greater than IClass\_LIM min as defined in Table 33–4a, the PSE shall classify the PD as Class 04. If any measured IMark is greater than or equal to IMark\_LIM min as defined in Table 33–4a, the PSE shall classify the PD as Class 0.

Subsequent to such classification, the PSE shall ensure that the voltage at the PI enters the VReset range for at least TReset min as definied in Table 33–4a prior to powering the port.

←Accept in principle OBE See 149

Comment Type TR Comment Status A

If the measured Iclass is greater than Iclass\_lim, the assigned class is Class4. There is no reason to reset the voltage at the PI in this case. Whithout this sentence, if the 2-event classification succeded, the PD will work correctly as class 4.

With a reset instead, the PD will work as a Type1 PD, wasting a lot of the allocated by the PSE.

SuggestedRemedy

Remove the sentence:

Subsequent to such classification, the PSE shall ensure that

the voltage at the PI enters the VReset range for at least TReset min as definied in Table 33–4a prior to powering the port.

Response

ACCEPT.

Response Status C

Cl 33 SC 2.7.2a P37 L52 # 129

Schindler, Fred Cisco Systems

Comment Type TR Comment Status A L1 adhoc

The same settling requirements for Type-1 classification should be imposed on Type-2 first class, classification. A Type 1 PD requires 5 ms to provide a valid class current (table 33-

SuggestedRemedy

Have the L1 ad hoc review and correct this section.

12, item 9). This comment also applies to p38 L24.

We have to wait until next draft to implement these enhancements.

The editor to apply the same transient settling timing to both 1-event and 2-event classifications. Page 37, line 43.

Comment 129 suggests 1-Event and 2-Event PSEs should have same time measurement delay requirement. Ad hoc agrees.

Modify comment 243: Accept in principle, but change wording p37L43: IS: Measurement to be taken after 6ms to ignore initial transients.

SHOULD BE: Measurement to be taken

after Tpdc to ignore initial transients.

ADD p37L54: Measurement to be taken after Tcle1 to ignore initial transients.

ADD p38L28: Measurement to be taken after Tcle2 to ignore initial transients.

C/ 33 SC 2.7.2 P37 L 43 Stanford, Clay Linear Technology Comment Type T Comment Status A The PSE is to wait either 6ms (2-event) or 10ms (1-event) before taking a Classification current reading. The text incorrectly says 1ms Change the value. See other comment suggesting aligning 2-event and 1-event timing. SuggestedRemedy Measurement of IClass shall be taken after 1 ms to ignore initial transients. Measurement of IClass shall be taken after 6 ms to ignore initial transients. Response Response Status C ACCEPT. see 164

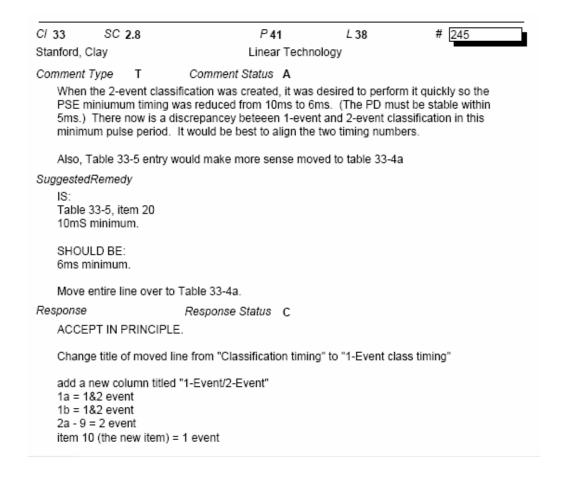

Comment 245 was accepted and suggested aligning Type 1 and Type 2 class timing. However, editor instructions do not this state explicitly. Ad hoc suggests Table 33-4a, entry 10 minimum time changed from 10ms to 6ms.

C/ 33 SC 3.4.2 P 57 L 50 # 111

Darshan, Yair Microsemi Corporation

Comment Type T Comment Status D

L1 adhoc

Draft 1.0:

PD don't have to present class 4 for infinite classification attempts.

ld adds thermal burden and costs.

In any case if system has problems it may initiate consecutive startups every Ted which is defined in Table 33-5 item 21.

#### SuggestedRemedy

To be added after line 50.

"PD may revert to IDLE state if PSE initiate more then 3 consecutive classification attempts within less then Ted as specified in Table 33-5."

Proposed Response

Response Status O

defer to L1

Sentence in Question: A Type 2 PD shall return a Class 4 signature irrespective of the number of classification voltage probes performed by a PSE.

Task force decided to strike the sentence completely.

C/ 33 SC 2.7.2a P38 L40 # 102

Darshan, Yair Microsemi Corporation

Comment Type TR Comment Status D L1 adhoc

Draft 1.0:

When PSE classify the PD after Iclas\_LIM event it should get to Vreset for Treset prior to power the port.

In order to achieve this objective PD should consume some minimum current to allow PSE to reduce its port voltage due the capacitors in the channel.

#### SuggestedRemedy

The classification ad hoc to address this issue if it is possible to implement i.e. to have I>>0 at 2.8V to 6.9 Volt range for Treset.

Proposed Response Response Status O

defer to L1

Accept in principle.

Add the following at p58L13

# The PD shall draw 0.25 mA minimum until the PD transitions from the Mark state to the Reset state.

We need to extend PSE Treset to insure port gets discharged.

dt = C dv/I = .7uf \* 4.2V/.25mA = 12msModify comment 267 (p39L30) from 5ms to 15ms.

This is OK with adhoc.

C/ 33 SC 2.7.2a P39 L30 # 267

Stanford, Clay Linear Technology

Comment Type T Comment Status A

Clarify Reset timing is only for 2-event classifiation and add timing parameter.

SuggestedRemedy

Table 33-4a Item 9

IS:

Classification Reset Timing|Treset|ms|TBD|TBD|blank

SHOULD BE:

Classification Reset Timing|Treset|ms|5|blank|blank

Response Response Status C ACCEPT.

CI 33

SC 2.7

P 36

L 27

# 127

Schindler, Fred

Cisco Systems

Comment Type

TR

Comment Status

D

L1 adhoc

The text:

"If a PSE successfully completes detection of a PD, but the PSE fails to complete classification of a PD, then a Type 1 PSE shall assign the PD to Class 0 and a Type 2 PSE shall assign the PD to class 4." imposes an unnecessary design requirement. This text also enables dump-Type 2 PDs that do not support DLL classification.

A system that does not provide a proper class is:

a) Experiencing a temporary fault that will rectify itself.

OR

b) Noncompliant.

A compliant Type-2 PD has not achieved mutual identification and will remain in type-1 power mode. Therefore, requiring class-4 power serves no legitimate purpose.

A PSE that classifies a PD and gets an invalid results is not probable because this occurs only when class current exceeds 51 mA.

#### SuggestedRemedy

Require PSEs that performs classification, to either repeat the detection and classification steps, or repeat the classification step, until legal responses are achieved.

Proposed Response

Response Status O

defer to L1

The task force decided to resolve this comment by stating the PSE behavior in this situation is undefined.

Will require full committee discussion.

Corrections to address the following issues will be commented on in the next draft.

# New Mark Timing Issue

PSE Mark Event timing

Table 33-4a, item 4 (D1.0, page 39, line 19)

- Though hardware as spec'ed will interoperate, port loading during event will effect observable timing behavior.

- Timing start and stop points are not clearly defined in standard.

- Due to lack of clear definition in standard, misinterpretation of timing could occur.

- Intent was for timing event to commence when PSE changes from Class mode to Mark mode.

- Intent was for timing event to end when PSE changes from Mark mode to Class mode.

# New Mark Timing Solution

#### 33.2.7.2a P38L21 TEXT IS:

The Type 2 PSE shall then provide to the PI VMark as defined in Table 33–4a. The timing specification shall be as defined by TME1 in Table 33–4a. This first VMark provision is known as the first mark event.

The Type 2 PSE shall then provide to the PI the second class event, subject to the VClass and TCLE2 definitions in Table 33–4a. The PSE shall measure IClass and again classify the PD based on the observed current according to Table 33–4.

Following successful completion of the second class event, the PSE shall provide a second mark event subject to the VMark and TME2 definitions in Table 33–4a.

#### 33.2.7.2a P38L21 TEXT SHOULD BE:

The Type 2 PSE shall then provide to the PI VMark as defined in Table 33–4a. This first VMark provision is known as the 1<sup>st</sup> mark event. The PI VMark requirement is to be met with load currents in the range of 0.25 to 2mA. In a properly operating PoE system, the port may or may not discharge to the VMark range due to the combination of channel capacitance and PD current loading. This is normal and acceptable PoE system operation. For compliance testing, it is necessary to discharge the port in order to observe the VMark voltage. Discharge can be accomplished with a 2mA load for 3mS, after which VMark can be observed with minimum and maximum load current.

The first mark event timing specification shall be as defined by TME1 in Table 33–4a. The mark event commences when the PI voltage falls below VClass\_min and ends when the PI voltage exceeds VClass\_min.

# New Mark Timing Solution Cont'

#### 33.2.7.2a P38L30 TEXT IS:

Following successful completion of the second class event, the PSE shall provide a second mark event subject to the VMark and TME2 definitions in Table 33–4a.

#### 33.2.7.2a P38L21 TEXT SHOULD BE:

Following successful completion of the second class event, the PSE shall provide a second mark event subject to the VMark and TME2 definitions in Table 33–4a. The mark event commences when the PI voltage falls below the VClass\_min and ends when the PI voltage exceeds VClass\_min. There is not a specified TME2\_max, however per 33.2.8.13, if the PSE is to power a PD, it is required to do so within Tpon.

# New Mark Timing Solution Cont'

Table 33-4a-Type 2 Physical Layer classification electrical requirements

| Item | Parameter                          | Symbol                 | Units | Min  | Max  | Additional<br>Information                                          |

|------|------------------------------------|------------------------|-------|------|------|--------------------------------------------------------------------|

| 1a   | Class Event Voltage                | V <sub>Class</sub>     | v     | 15.5 | 20.5 |                                                                    |

| 1b   | Class Event Current Limitation     | I <sub>Class_LIM</sub> | mA    | 51   | 100  |                                                                    |

| 2a   | Mark Event Voltage                 | $V_{\mathrm{Mark}}$    | V     | 7    | 10   | 0.25mA≤lLoad≤2mA<br>See 33.2.7.2a                                  |

| 2b   | Mark Event Current Limitation      | $I_{Mark\_LIM}$        | mA    | 5    | 100  |                                                                    |

| 3    | 1st Class Event Timing             | T <sub>CLE1</sub>      | ms    | 6    | 30   |                                                                    |

| 4    | 1 <sup>st</sup> Mark Event Timing  | T <sub>ME1</sub>       | ms    | 6    | 12   | See 33.2.7.2a                                                      |

| 5    | 2 <sup>nd</sup> Class Event Timing | T <sub>CLE2</sub>      | ms    | 6    | 30   |                                                                    |

| 6    | 2 <sup>nd</sup> Mark Event Timing  | T <sub>ME2</sub>       | ms    | 6    |      | Time from end of detection until power on is limited by 33.2.8.13. |

| 7    | 3 <sup>rd</sup> Class Event Timing | T <sub>CLE3</sub>      | ms    |      | 30   |                                                                    |

| 8    | Classification Reset Voltage       | $V_{Reset}$            | V     | 0    | 2.8  |                                                                    |

| 9    | Classification Reset Timing        | T <sub>Reset</sub>     | ms    | TBD  | TBD  |                                                                    |

See 33.2.7.2a

### New PD Class to Mark Current Issue

- The required current draw of the PD as it transitions from Class to Mark is not clearly defined.

- The PD must continue to draw current in order for the port to discharge.

- We will add text to clarify the operation in this range.

# New PD Class to Mark Solution

#### P57L50 TEXT IS (with implementation of accepted and expected comments)

#### 33.3.4.2.1 Mark Event behavior

When the voltage at the PI is within the range of VMark, a Type 2 PD shall return a non-valid detection signature as defined in Table 33–9.

A Type 2 PD must return a Class 4 signature when voltage at the PI is in the range of Vclass. A Type 2 PD must draw IMark when voltage at the PI is in the range of VMark.

A Type 2 PD shall not exceed the IMark current limits when voltage at the PI enters the VMark specification as defined in Table 33–11a.

## P57L50 TEXT SHOULD BE(with implementation of accepted and expected comments) 33.3.4.2.1 Mark Event behavior

When the voltage at the PI is within the range of VMark, a Type 2 PD shall return a non-valid detection signature as defined in Table 33–9.

A Type 2 PD must return a Class 4 signature when voltage at the PI is in the range of Vclass. A Type 2 PD must draw IMark when voltage at the PI is in the range of VMark.

A Type 2 PD shall not exceed the IMark current limits when voltage at the PI enters the VMark specification as defined in Table 33–11a.

As the PD is changing from Class to Mark state, it shall transition from the Class 4 signature current to the Mark current. This transition shall occur in the range of Vmark\_th. During this transition, the PD shall draw at least IMark\_min current.

During discussion in the task force, it was suggested that comment 120 addresses this issue for layer 1 classification.

# New Turn On Delay Issue

- When a Type 2 PD is powered, it is powered up with Type 1 current and power limits.

- After power up, the PSE transitions the power supply from Type 1 level to Type 2 level.

- The time when this occurs will depend on the classification type.

- 2-Event classification will allow system to transition soon after power\_on.

- 1-Event + Layer 2 classification will take longer time period (1-2 minutes?) before the change is made.

- Finite time is required for PSE to make transition from low power to high power state.

- When using 2-event classification, PD must wait until PSE transition from low power to high power is complete before drawing higher current.

- This timing requirement is not currently specified in the standard.

- We need to add a low-power to high-power transition delay in the PD section.

- When using layer 2 classification, this issue can be addressed by the order in which the PSE executes events. The PSE can transition to high power before granting high power to the PD.

- To insure proper operation, we should specify this in the Layer 2 classification section.

C/ 33 SC 3.5.3 P61 L9 # 120

Vetteth, Anoop Cisco

Comment Type TR Comment Status A

There is no shall statement in this section that mandates that all Type-2 PDs have to satisfy the same inrush criterion as Type-1 PDs.

#### SuggestedRemedy |

Add text:

Type 2 PDs with pse\_power\_type state variable set to type 2 prior to power-ON shall behave like a type 1 PD during the startup period.

Response Status C

ACCEPT IN PRINCIPLE.

Add text:

Type 2 PDs with pse\_power\_type state variable set to type 2 prior to power-ON shall behave like a type 1 PD for at least Tinrush max as defined in Table 33-5.

Add Tinrush to Table 33-5, item 5a, Inrush time/TinrushIms/50/75/1,2/see 33.2.8.5