| Replace Clause 33:                                                          | 1<br>2           |

|-----------------------------------------------------------------------------|------------------|

| 33. Data Terminal Equipment (DTE) Power via Media Dependent Interface (MDI) | 3<br>4<br>5<br>6 |

| 33.1 Overview                                                               | 7<br>8<br>9      |

| 33.2 Power sourcing equipment                                               | 10<br>11         |

| 33.2.1 PSE location                                                         | 12<br>13         |

| 33.2.2 Midspan PSE types                                                    | 13<br>14<br>15   |

| 33.2.3 PI pin assignments                                                   | 16<br>17         |

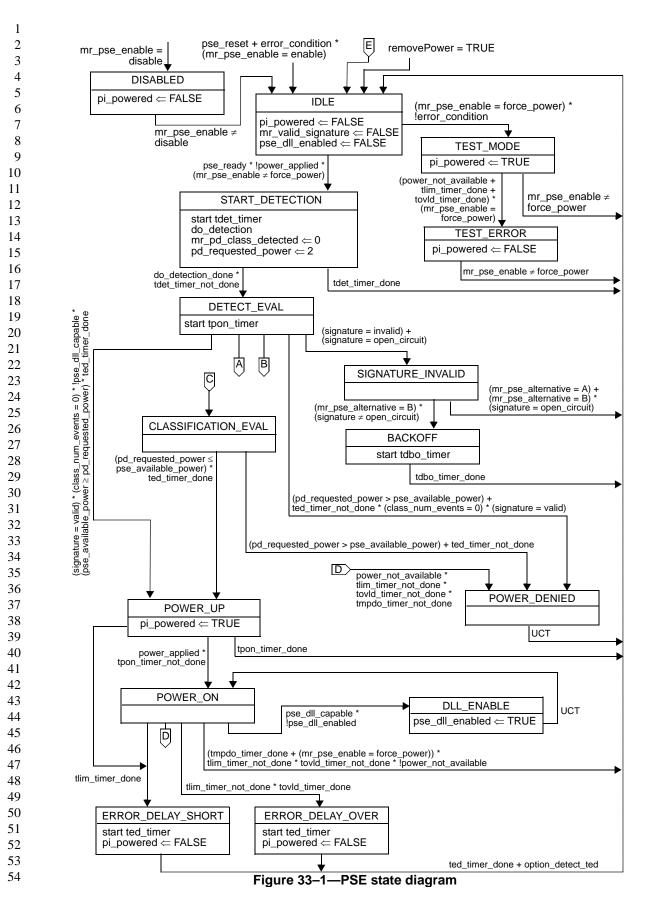

| 33.2.4 PSE state diagrams                                                   | 17<br>18<br>19   |

| 33.2.4.1 Overview                                                           | 20               |

| 33.2.4.2 Conventions                                                        | 21<br>22         |

| 33.2.4.3 Constants                                                          | 23<br>24         |

| 33.2.4.4 Variables                                                          | 25<br>26         |

| 33.2.4.5 Timers                                                             | 27<br>28         |

| 33.2.4.6 Functions                                                          | 29<br>30         |

| 33.2.4.7 State diagrams                                                     | 31<br>32         |

|                                                                             | 33<br>34         |

|                                                                             | 35<br>36         |

|                                                                             | 37               |

|                                                                             | 38<br>39         |

|                                                                             | 39<br>40         |

|                                                                             | 41               |

|                                                                             | 42               |

|                                                                             | 43<br>44         |

|                                                                             | 45               |

|                                                                             | 46               |

|                                                                             | 47<br>48         |

|                                                                             | 48<br>49         |

|                                                                             | 50               |

|                                                                             | 51               |

|                                                                             | 52<br>53         |

|                                                                             | 53<br>54         |

# 33.3 Powered devices

# 33.4 Additional electrical specifications

# 33.5 Environmental

# **33.6 Management function requirements**

# 33.7 Data Link Layer classification

# [EDITOR'S NOTE—Update the below noted 802.1AB reference to reflect the proper revision during preparation for publication.]

Additional control and classification functions are supported using Data Link Layer classification using frames based on the IEEE 802.3 Organizationally Specific TLVs defined in Annex G of IEEE Std 802.1AB<sup>TM</sup>-200X protocol (LLDP). Type 2 PDs that require more than 12.95 W must support Data Link Layer classification (see 33.3.5). Data Link Layer classification is optional for all other devices.

# 33.7.1 TLV frame definition

Implementations that support Data Link Layer classification shall comply with all mandatory parts of IEEE Std 802.1AB<sup>TM</sup>-200X; shall support the DTE Power via MDI classification Type, Length, Value (TLV) defined in 33.7.2; and shall support the control state diagrams defined in 33.7.6.

A device implementing Data Link Layer classification shall send power management Protocol Data Units (PDUs) and process PDUs received from the remote device at least once every 30 seconds. Each power management PDU shall contain the DTE Power via MDI classification TLV.

# 33.7.2 DTE Power via MDI classification TLV

The DTE Power via MDI classification TLV is used to perform Data Link Layer classification. Figure 33–2 shows the format of this TLV.

| TLV<br>type = 127 | TLV information<br>string length = 10 | 802.3 OUI<br>00-12 <mark>-</mark> 0F | 802.3<br>subtype = <u>TBD</u> | Type/<br>source/priority | PD<br>Requested<br>power value | PSE<br>Allocated<br>power value | Loss<br>of<br>Commuication |

|-------------------|---------------------------------------|--------------------------------------|-------------------------------|--------------------------|--------------------------------|---------------------------------|----------------------------|

| 7 bits            | 9 bits                                | 3 octets                             | 1 octet                       | 1 octet                  | 2 octets                       | 2 octets                        | 1 octet                    |

| <b>—</b> т        | LV header —                           | -                                    |                               | TLV info                 | rmation string                 |                                 |                            |

Figure 33–2—DTE Power via MDI classification TLV format

The information supplied by the Power Via MDI TLV defined in IEEE Std 802.1AB<sup>™</sup> Annex G.3 is superseded by the DTE Power via MDI classification TLV. Based on this, in order to conserve LLDPDU space, when the DTE Power via MDI classification TLV is being transmitted, the Power via MDI TLV shall not be transmitted.

# 33.7.2.1 Requested power type/source/priority

The power type/source/priority field shall contain a bit-map of the power type, source and priority defined in Table 33–1.

| Bit | Function       | Value/meaning                                                                                                                                                                                                                         |

|-----|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:6 | power type     | $\begin{array}{rrrrrrrrrrrrrrrrrrrrrrrrrrrrrrrrrrrr$                                                                                                                                                                                  |

| 5:4 | power source   | Where power type = PD<br>5 $41$ $1$ = PSE and local<br>1 $0$ = Local<br>0 $1$ = PSE<br>0 $0$ = Unknown<br>Where power type = PSE<br>5 $41$ $1$ = Reserved<br>1 $0$ = Backup source<br>0 $1$ = Primary power source<br>0 $0$ = Unknown |

| 3:2 | Reserved       | Reserved                                                                                                                                                                                                                              |

| 1:0 | power priority | $\begin{array}{cccc} \underline{1} & \underline{0} \\ 1 & 1 & = \text{low} \\ 1 & 0 & = \text{high} \\ 0 & 1 & = \text{critical} \\ 0 & 0 & = \text{unknown (default)} \end{array}$                                                   |

# Table 33–1—Power type/source/priority field

# 33.7.2.1.1 Power type

This field shall be set to 01 for a PD (see 33.3) and 00 for a PSE (see 33.2).

# 33.7.2.1.2 Power source

When the power type is PD, this field shall be set to 01 when the PD is being powered only through the PI; to 10 when the PD is being powered only from a local supply; to 11 when the PD is being powered from both; and to 00 when this information is not available.

When the power type is PSE, this field shall be set to 01 when the PSE is sourcing its power through the PI from its primary supply; to 10 when the PSE is sourcing its power through the PI from a backup source; and to 00 when this information is not available.

# 33.7.2.1.3 Power priority

When the power type is PD, this field shall be set to the power priority configured for the device. If a PD is unable to determine its power priority or it has not been configured, then this field shall be set to 00.

When the power type is PSE, this field shall be set to 00.

(0-1)

# 33.7.2.2 Requested PD power value

The requested power value field shall contain the PD's requested power value defined in Table 33–2.

#### Table 33–2—Power value field

| Bit  | Function       | Value/meaning                                                                                                 |

|------|----------------|---------------------------------------------------------------------------------------------------------------|

| 15:0 | PD power value | Power = $0.1 \times$ (decimal value of bits) Watts.<br>Valid values for these bits are decimal 0 through 295. |

The PD power value is encoded according to the following formula:

$\{Power = (0.1 \times X)\}_{Watts}$

where

Poweris the effective requested PD power valueXis the decimal value of the power value field, bits 15:0

This power is always the power at the input of the PD's PI, and so does not include channel losses. In the ease of a PSE, this power is the power at the output of the PSE's PI. The PSE is therefore responsible for estimating and including channel loss when calculating the PSE allocated port power value.

If accepted by the PSE, the requested PD power value for a PD is the new maximum input average power (see 33.3.7.2) the PD will ever draw under this power allocation. If accepted by the PD, the PD requested power value for a PSE is the new maximum input average power it wants the PD to ever draw under this power allocation.

#### 33.7.2.3 Actual power type/source/priority

The actual power type/source/priority field shall contain a bit-map of the actual power type, source, and priority defined in Table 33–1.

#### 33.7.2.4 Actual PD power value

The PD actual power value field shall contain the current actual PD power value defined in Table 33-2.

The actual PD power value for a PD is the maximum input average power (see 33.3.7.2) the PD will ever draw under the current power allocation. The actual PD power value for a PSE is the maximum input average power the PD may ever draw under the current power allocation.

### 33.7.2.5 Loss of Communication

The Loss of Communcation field shall contain a value to indicate that the device believes it has lost communication with the far end. The encoding of this field is defined in Table 33–3.

| Bit | Function | Value/meaning                                                |

|-----|----------|--------------------------------------------------------------|

| 7:1 | reserved | reserved                                                     |

| 0   |          | 1 = loss of communications<br>0 = communication OK (default) |

### Table 33–3—Loss of Communication field

# 33.7.3 DTE Power via MDI classification TLV to local PSE object class cross references

The cross references between the DTE power via MDI classification TLV and the DTE Power via MDI classification local object class (30.9.1) attributes are listed in Table 33–4.

# Table 33–4—DTE power via MDI classification TLV to PSE object class cross references

| TLV name                         | TLV variable              | Attribute                         |

|----------------------------------|---------------------------|-----------------------------------|

| DTE power via MDI classification | power type                | aDLLPowerType                     |

| ·                                | power Source              | aDLLPowerSource                   |

| ·                                | power priority            | RESERVED                          |

|                                  | PD Requested power value  | aMirroredDLLPDRequestedPowerValue |

|                                  | PSE Allocated power value | aDLLPSEAllocatedPowerValue        |

| ·                                | Loss of Communication     | aLostCommunication                |

# 33.7.4 DTE Power via MDI classification TLV to remote object class cross references

The cross references between the DTE power via MDI classification TLV and the DTE Power via MDI classification PD object class (30.9.2) attributes are listed in Table 33–5.

# Table 33–5—DTE power via MDI classification TLV to PD object cross references

| TLV name                         | TLV variable              | Clause 30 attribute                |

|----------------------------------|---------------------------|------------------------------------|

| DTE power via MDI classification | power type                | aDLLPowerType                      |

|                                  | power Source              | aDLLPowerSource                    |

|                                  | power priority            | aDLLPDPowerPriority                |

| -                                | PD Requested power value  | aDLLPDRequestedPowerValue          |

| -                                | PSE Allocated power value | aMirroredDLLPSEAllocatedPowerValue |

|                                  | Loss of Communication     | aLostCommunication                 |

# 33.7.5 Data Link Layer classification timing requirements

An LLDPDU containing a DTE Power via MDI classification TLV shall be sent within 5 minutes of Data Link Layer classification being enabled in a PD as indicated by the variable pd\_dll\_enabled, or in a PSE as indicated by the variable pse\_dll\_enabled. See 33.2.4.4, 33.3.3.3, 33.7.6.2.

An LLDPDU containing a DTE Power via MDI classification TLV with the Acknowledge field set to either "acknowledge" or "non-acknowledge" shall be sent within 5 minutes of an LLDPDU containing a DTE Power via MDI classification TLV being received with the Requested power value field not equal to the Actual power value field.

An LLDPDU containing a DTE Power via MDI classification TLV with the Acknowledge field set to "not

part of acknowledge cycle" shall be sent within 5 minutes of an LLDPDU containing a DTE Power via MDI

classification TLV. with the Acknowledge field set to either "acknowledge" or "non-acknowledge."

# 33.7.6 Power control state diagrams

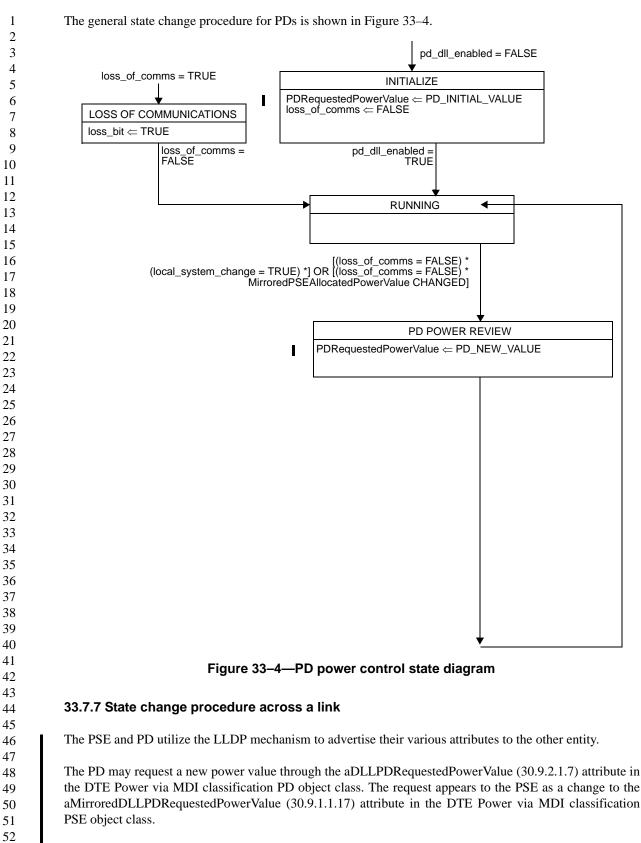

The power control state diagrams for PSEs and PDs specify the externally observable behavior of a PSE and PD Data Link Layer classification respectively. PSE Data Link Layer classification shall provide the behavior of the state diagram as shown in Figure 33–3. PD Data Link Layer classification shall provide the behavior of the state diagram as shown in Figure 33–4.

# 33.7.6.1 Conventions

The body of this subclause is comprised of state diagrams, including the associated definitions of variables, constants, and functions. Should there be a discrepancy between a state diagram and descriptive text, the state diagram prevails.

The notation used in the state diagrams follows the conventions of state diagrams as described in 21.5.

### 33.7.6.2 Variables

The PSE power control state diagram (Figure 33–3) and PD power control state diagram (Figure 33–4) use the following variables:

| the following var | laules.                |                                                                                  | 1) |

|-------------------|------------------------|----------------------------------------------------------------------------------|----|

| -                 |                        |                                                                                  | 20 |

| locAcknowled      | <del>ge</del>          |                                                                                  | 21 |

| Indicate          | s the respo            | onse of the local system to the remote system's last change in requested power-  | 22 |

| value. T          | <del>his variabl</del> | e is mapped to the aLLDPPoEPLocAcknowledge attribute (30.12.1.1.10).             | 23 |

| Values:           | LOSS:                  | The local system has detected a loss of communication. This value maps to        | 24 |

|                   |                        | the enumeration "loss of communications."                                        | 25 |

|                   | NACK:                  | The local system has not accepted the requested change to the allocated          | 26 |

|                   |                        | power. This value maps to the enumeration "non-acknowledge."                     | 27 |

|                   | ACK:                   | The local system has accepted the requested change to the allocated power.       | 28 |

|                   |                        | This value maps to the enumeration "acknowledge."                                | 29 |

|                   | NULL:                  | There is no requested change to the allocated power. This value maps to the      | 30 |

|                   |                        | enumeration "not part of acknowledge cycle."                                     | 31 |

| locActualPowe     | er Value               |                                                                                  | 32 |

| Integer that      | at indicates           | the actual PD power value of the local system. The actual PD power value for a   | 33 |

| PD is the         | maximum                | input average power (see 33.3.7.2) the PD will ever draw under the current       | 34 |

| power alle        | cation. The            | e actual PD power value for a PSE is the maximum input average power the PD      | 35 |

| may ever          | draw unde              | r the current power allocation. The PD power value is encoded according to       | 36 |

| Equation (        | 0-1), wher             | e X is the decimal value of locActualPowerValue. This variable is mapped to the  | 37 |

| aLLDPPo           | EPLocActu              | ualPDPowerValue attribute (30.12.1.1.9).                                         | 38 |

| Values:           | 0 throug               | h 295.                                                                           | 39 |

| local_system_o    | change                 |                                                                                  | 40 |

| An imp            | lementation            | n specific control variable that indicates that the local system wants to change | 41 |

| the lock          | RequestedP             | owerValue.                                                                       | 42 |

| Values:           | FALSE:                 | The local system does not wants to change the locRequestedPowerValue.            | 43 |

|                   | TRUE:                  | The local system wants to change the locRequestedPowerValue.                     | 44 |

| locRequestedP     | <del>owerValue</del>   |                                                                                  | 45 |

|                   |                        | tes the requested PD power value of the local system. The requested PD power     | 46 |

|                   |                        | the new maximum input average power (see 33.3.7.2) the PD will ever draw         | 47 |

|                   | -                      | llocation if it is accepted. The PD requested power value for a PSE is the new   | 48 |

| maximu            | <del>ım input av</del> | verage power it wants the PD to ever draw under this power allocation if it is   | 49 |

| accepte           | d. The PD              | power value is encoded according to Equation (0-1), where X is the decimal       | 50 |

|                   | -                      | stedPowerValue. This variable is mapped to the aLLDPPoEPLocRequestedPD-          | 51 |

| PowerV            | alue attribu           | <del>ate (30.12.1.1.5).</del>                                                    | 52 |

|                   | 0 throug               |                                                                                  | 53 |

| PDRequestedP      | owerValue              |                                                                                  | 54 |

|                   |                        |                                                                                  |    |

| ariable is mapped from<br>ocated power value in th<br>PD will ever draw. The<br>ever draw. The PD power<br>e of PSEAllocatedPower<br>ttribute (30.9.1.1.18).<br>rValue that the PD has.<br>ariable is mapped from<br>E: This value is derived to                                                                        | s. The definition is the same as<br>the aMirroredDLLPDRequested<br>are PSE. The value is the maximum<br>power value for a PSE is the ma<br>r value is encoded according to E<br>rValue. This variable is mapped for<br>. The definition is the same as<br>the aMirroredDLLPSEAllocated<br>from the mr_pd_class_detected we<br>e diagram (Figure 33–1) as follow          |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ariable is mapped from<br>ocated power value in th<br>PD will ever draw. The<br>ever draw. The PD power<br>e of PSEAllocatedPower<br>ttribute (30.9.1.1.18).<br>rValue that the PD has.<br>ariable is mapped from<br>C: This value is derived to<br>output by the PSE state<br>mr_pd_class_detected<br>0<br>1<br>2<br>3 | the aMirroredDLLPDRequested<br>the PSE. The value is the maximu<br>power value for a PSE is the ma<br>r value is encoded according to E<br>rValue. This variable is mapped f<br>. The definition is the same as<br>the aMirroredDLLPSEAllocated<br>from the mr_pd_class_detected v<br>e diagram (Figure 33–1) as follow<br>1 PSE_INITIAL_VALUE<br>130<br>39<br>65<br>130 |

| ariable is mapped from<br>ocated power value in th<br>PD will ever draw. The<br>ever draw. The PD power<br>e of PSEAllocatedPower<br>ttribute (30.9.1.1.18).<br>rValue that the PD has.<br>ariable is mapped from<br>C: This value is derived to<br>output by the PSE state<br>mr_pd_class_detected<br>0<br>1<br>2<br>3 | the aMirroredDLLPDRequested<br>the PSE. The value is the maximu<br>power value for a PSE is the mar<br>r value is encoded according to E<br>rValue. This variable is mapped f<br>. The definition is the same as<br>the aMirroredDLLPSEAllocated<br>from the mr_pd_class_detected<br>e diagram (Figure 33–1) as follow<br>1 PSE_INITIAL_VALUE<br>130<br>39<br>65<br>130  |

| ariable is mapped from<br>ocated power value in th<br>PD will ever draw. The<br>ever draw. The PD power<br>e of PSEAllocatedPower<br>ttribute (30.9.1.1.18).<br>rValue that the PD has.<br>ariable is mapped from<br>C: This value is derived to<br>output by the PSE state<br>mr_pd_class_detected<br>0<br>1<br>2<br>3 | the aMirroredDLLPDRequested<br>the PSE. The value is the maximu<br>power value for a PSE is the mar<br>r value is encoded according to E<br>rValue. This variable is mapped f<br>. The definition is the same as<br>the aMirroredDLLPSEAllocated<br>from the mr_pd_class_detected<br>e diagram (Figure 33–1) as follow<br>1 PSE_INITIAL_VALUE<br>130<br>39<br>65<br>130  |

| Decated power value in th<br>PD will ever draw. The<br>ever draw. The PD power<br>e of PSEAllocatedPower<br>ttribute (30.9.1.1.18).<br>rValue that the PD has<br>ariable is mapped from<br>E: This value is derived in<br>output by the PSE state<br>mr_pd_class_detected<br>0<br>1<br>2<br>3                           | the PSE. The value is the maximu<br>power value for a PSE is the mar<br>r value is encoded according to E<br>rValue. This variable is mapped for<br>. The definition is the same as<br>the aMirroredDLLPSEAllocated<br>from the mr_pd_class_detected<br>e diagram (Figure 33–1) as follow<br>1 PSE_INITIAL_VALUE<br>130<br>39<br>65<br>130                               |

| PD will ever draw. The<br>ever draw. The PD power<br>e of PSEAllocatedPower<br>ttribute (30.9.1.1.18).<br>rValue that the PD has.<br>ariable is mapped from<br>C: This value is derived to<br>output by the PSE state<br>mr_pd_class_detected<br>0<br>1<br>2<br>3                                                       | power value for a PSE is the m<br>r value is encoded according to E<br>r Value. This variable is mapped f<br>. The definition is the same as<br>the aMirroredDLLPSEAllocated<br>from the mr_pd_class_detected<br>e diagram (Figure 33–1) as follow<br>1 PSE_INITIAL_VALUE<br>130<br>39<br>65<br>130                                                                      |

| PD will ever draw. The<br>ever draw. The PD power<br>e of PSEAllocatedPower<br>ttribute (30.9.1.1.18).<br>rValue that the PD has.<br>ariable is mapped from<br>C: This value is derived to<br>output by the PSE state<br>mr_pd_class_detected<br>0<br>1<br>2<br>3                                                       | power value for a PSE is the m<br>r value is encoded according to E<br>r Value. This variable is mapped f<br>. The definition is the same as<br>the aMirroredDLLPSEAllocated<br>from the mr_pd_class_detected<br>e diagram (Figure 33–1) as follow<br>1 PSE_INITIAL_VALUE<br>130<br>39<br>65<br>130                                                                      |

| PD will ever draw. The<br>ever draw. The PD power<br>e of PSEAllocatedPower<br>ttribute (30.9.1.1.18).<br>rValue that the PD has.<br>ariable is mapped from<br>C: This value is derived to<br>output by the PSE state<br>mr_pd_class_detected<br>0<br>1<br>2<br>3                                                       | power value for a PSE is the m<br>r value is encoded according to E<br>r Value. This variable is mapped for<br>. The definition is the same as<br>the aMirroredDLLPSEAllocated<br>from the mr_pd_class_detected<br>e diagram (Figure 33–1) as follow<br>1 PSE_INITIAL_VALUE<br>130<br>39<br>65<br>130                                                                    |

| PD will ever draw. The<br>ever draw. The PD power<br>e of PSEAllocatedPower<br>ttribute (30.9.1.1.18).<br>rValue that the PD has.<br>ariable is mapped from<br>C: This value is derived to<br>output by the PSE state<br>mr_pd_class_detected<br>0<br>1<br>2<br>3                                                       | power value for a PSE is the m<br>r value is encoded according to E<br>r Value. This variable is mapped for<br>. The definition is the same as<br>the aMirroredDLLPSEAllocated<br>from the mr_pd_class_detected<br>e diagram (Figure 33–1) as follow<br>1 PSE_INITIAL_VALUE<br>130<br>39<br>65<br>130                                                                    |

| ever draw. The PD power<br>e of PSEAllocatedPower<br>ttribute (30.9.1.1.18).<br>rValue that the PD has,<br>ariable is mapped from<br>C: This value is derived to<br>output by the PSE state<br>mr_pd_class_detected<br>0<br>1<br>2<br>3                                                                                 | r value is encoded according to E<br>rValue. This variable is mapped to<br>. The definition is the same as<br>the aMirroredDLLPSEAllocated<br>from the mr_pd_class_detected<br>e diagram (Figure 33–1) as follow<br>1 PSE_INITIAL_VALUE<br>130<br>39<br>65<br>130                                                                                                        |

| e of PSEAllocatedPowe<br>ttribute (30.9.1.1.18).<br>rValue that the PD has<br>ariable is mapped from<br>E: This value is derived in<br>output by the PSE state<br>mr_pd_class_detected<br>0<br>1<br>2<br>3                                                                                                              | rValue. This variable is mapped to<br>. The definition is the same as<br>the aMirroredDLLPSEAllocated<br>from the mr_pd_class_detected<br>e diagram (Figure 33–1) as follow<br>d PSE_INITIAL_VALUE<br>130<br>39<br>65<br>130                                                                                                                                             |

| ttribute (30.9.1.1.18).<br>rValue that the PD has<br>ariable is mapped from<br>E: This value is derived is<br>output by the PSE state<br>mr_pd_class_detected<br>0<br>1<br>2<br>3                                                                                                                                       | . The definition is the same as<br>the aMirroredDLLPSEAllocated<br>from the mr_pd_class_detected<br>e diagram (Figure 33–1) as follor<br>1 PSE_INITIAL_VALUE<br>130<br>39<br>65<br>130                                                                                                                                                                                   |

| rValue that the PD has,<br>ariable is mapped from<br>E: This value is derived to<br>output by the PSE state<br>mr_pd_class_detected<br>0<br>1<br>2<br>3                                                                                                                                                                 | the aMirroredDLLPSEAllocated<br>from the mr_pd_class_detected<br>e diagram (Figure 33–1) as follor<br>1 PSE_INITIAL_VALUE<br>130<br>39<br>65<br>130                                                                                                                                                                                                                      |

| ariable is mapped from<br>This value is derived is<br>output by the PSE state<br>mr_pd_class_detected<br>0<br>1<br>2<br>3                                                                                                                                                                                               | the aMirroredDLLPSEAllocated<br>from the mr_pd_class_detected<br>e diagram (Figure 33–1) as follor<br>1 PSE_INITIAL_VALUE<br>130<br>39<br>65<br>130                                                                                                                                                                                                                      |

| ariable is mapped from<br>This value is derived is<br>output by the PSE state<br>mr_pd_class_detected<br>0<br>1<br>2<br>3                                                                                                                                                                                               | the aMirroredDLLPSEAllocated<br>from the mr_pd_class_detected<br>e diagram (Figure 33–1) as follor<br>1 PSE_INITIAL_VALUE<br>130<br>39<br>65<br>130                                                                                                                                                                                                                      |

| ariable is mapped from<br>This value is derived is<br>output by the PSE state<br>mr_pd_class_detected<br>0<br>1<br>2<br>3                                                                                                                                                                                               | the aMirroredDLLPSEAllocated<br>from the mr_pd_class_detected<br>e diagram (Figure 33–1) as follor<br>1 PSE_INITIAL_VALUE<br>130<br>39<br>65<br>130                                                                                                                                                                                                                      |

| E: This value is derived a<br>output by the PSE state<br>mr_pd_class_detected<br>0<br>1<br>2<br>3                                                                                                                                                                                                                       | from the mr_pd_class_detected<br>e diagram (Figure 33–1) as follor<br>1 PSE_INITIAL_VALUE<br>130<br>39<br>65<br>130                                                                                                                                                                                                                                                      |

| output by the PSE state<br>mr_pd_class_detected<br>0<br>1<br>2<br>3                                                                                                                                                                                                                                                     | e diagram (Figure 33–1) as follo<br>1 PSE_INITIAL_VALUE<br>130<br>39<br>65<br>130                                                                                                                                                                                                                                                                                        |

| output by the PSE state<br>mr_pd_class_detected<br>0<br>1<br>2<br>3                                                                                                                                                                                                                                                     | e diagram (Figure 33–1) as follo<br>1 PSE_INITIAL_VALUE<br>130<br>39<br>65<br>130                                                                                                                                                                                                                                                                                        |

| output by the PSE state<br>mr_pd_class_detected<br>0<br>1<br>2<br>3                                                                                                                                                                                                                                                     | e diagram (Figure 33–1) as follo<br>1 PSE_INITIAL_VALUE<br>130<br>39<br>65<br>130                                                                                                                                                                                                                                                                                        |

| mr_pd_class_detected<br>0<br>1<br>2<br>3                                                                                                                                                                                                                                                                                | 1 PSE_INITIAL_VALUE<br>130<br>39<br>65<br>130                                                                                                                                                                                                                                                                                                                            |

| 0<br>1<br>2<br>3                                                                                                                                                                                                                                                                                                        | 130<br>39<br>65<br>130                                                                                                                                                                                                                                                                                                                                                   |

| 1<br>2<br>3                                                                                                                                                                                                                                                                                                             | 39<br>65<br>130                                                                                                                                                                                                                                                                                                                                                          |

| 2 3                                                                                                                                                                                                                                                                                                                     | 65<br>130                                                                                                                                                                                                                                                                                                                                                                |

| 3                                                                                                                                                                                                                                                                                                                       | 130                                                                                                                                                                                                                                                                                                                                                                      |

|                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                          |

| 4                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                          |

| 0                                                                                                                                                                                                                                                                                                                       | 130                                                                                                                                                                                                                                                                                                                                                                      |

| 1                                                                                                                                                                                                                                                                                                                       | 39                                                                                                                                                                                                                                                                                                                                                                       |

| 2                                                                                                                                                                                                                                                                                                                       | 65                                                                                                                                                                                                                                                                                                                                                                       |

| 3                                                                                                                                                                                                                                                                                                                       | 130                                                                                                                                                                                                                                                                                                                                                                      |

| J<br>4                                                                                                                                                                                                                                                                                                                  | 255                                                                                                                                                                                                                                                                                                                                                                      |

| This value is derived t                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                          |

|                                                                                                                                                                                                                                                                                                                         | -                                                                                                                                                                                                                                                                                                                                                                        |

|                                                                                                                                                                                                                                                                                                                         | PD_INITIAL_VALUE                                                                                                                                                                                                                                                                                                                                                         |

|                                                                                                                                                                                                                                                                                                                         | 130                                                                                                                                                                                                                                                                                                                                                                      |

| 1                                                                                                                                                                                                                                                                                                                       | 39                                                                                                                                                                                                                                                                                                                                                                       |

| 2                                                                                                                                                                                                                                                                                                                       | 65                                                                                                                                                                                                                                                                                                                                                                       |

| 3                                                                                                                                                                                                                                                                                                                       | 130                                                                                                                                                                                                                                                                                                                                                                      |

| 4                                                                                                                                                                                                                                                                                                                       | 130                                                                                                                                                                                                                                                                                                                                                                      |

| 0                                                                                                                                                                                                                                                                                                                       | 130                                                                                                                                                                                                                                                                                                                                                                      |

| 1                                                                                                                                                                                                                                                                                                                       | 39                                                                                                                                                                                                                                                                                                                                                                       |

| 2                                                                                                                                                                                                                                                                                                                       | 65                                                                                                                                                                                                                                                                                                                                                                       |

| - 3                                                                                                                                                                                                                                                                                                                     | 130                                                                                                                                                                                                                                                                                                                                                                      |

| 4                                                                                                                                                                                                                                                                                                                       | 255                                                                                                                                                                                                                                                                                                                                                                      |

| This is the new value                                                                                                                                                                                                                                                                                                   | of power that the PSE allocate                                                                                                                                                                                                                                                                                                                                           |

| PD.                                                                                                                                                                                                                                                                                                                     | · · · · · · · · · · · · · · · · · · ·                                                                                                                                                                                                                                                                                                                                    |

|                                                                                                                                                                                                                                                                                                                         | of power that the PD wants to re-                                                                                                                                                                                                                                                                                                                                        |

|                                                                                                                                                                                                                                                                                                                         | PD.                                                                                                                                                                                                                                                                                                                                                                      |

Indicates if a loss of management frame communication defined in 33.8 has occurred.

| Value            | s: FALSE:                      | A loss of communications defined in 33.8 has not occurred.                     | 1  |

|------------------|--------------------------------|--------------------------------------------------------------------------------|----|

|                  | TRUE:                          | A loss of communications defined in 33.8 has occurred.                         | 2  |

| pd_dll_enab      | led                            |                                                                                | 3  |

| A va             | iable output                   | by the PD state diagram (Figure 33-4) to indicate if the PD Data Link Layer    | 4  |

| classi           | fication mecl                  | hanism is enabled.                                                             | 5  |

| Value            | s: FALSE:                      | PD Data Link Layer classification is not enabled.                              | 6  |

|                  | TRUE:                          | PD Data Link Layer classification is enabled.                                  | 7  |

| pse_dll_enal     | oled                           |                                                                                | 8  |

| A vai            | iable output                   | by the PSE state diagram (Figure 33–1) to indicate if the PSE Data Link Layer  | 9  |

| classi           | fication mecl                  | hanism is enabled.                                                             | 10 |

| Value            | s: FALSE:                      | PSE Data Link Layer classification is not enabled.                             | 11 |

|                  | TRUE:                          | PSE Data Link Layer classification is enabled.                                 | 12 |

| pse_power_o      | cycles                         |                                                                                | 13 |

| Indic            | ates whether                   | the PSE performs power cycling after a loss of management frame communica-     | 14 |

| tion (           | see 33.8).                     |                                                                                | 15 |

| Value            | s: FALSE:                      | PSE does not power cycle after loss of communications defined in 33.8.         | 16 |

|                  | TRUE:                          | PSE does power cycle after loss of communications defined in 33.8.             | 17 |

| remAcknow        | ledge                          |                                                                                | 18 |

| Indic            | ates the respo                 | mse from the remote system to the local systems last change in requested power | 19 |

| value            | <del>. This variab</del> l     | e is mapped from the aLLDPPoEPRemAcknowledge attribute (30.12.2.1.10).         | 20 |

| - Value          | <del>s:</del> <del>LOSS:</del> | The remote system has detected a loss of communication. This value maps        | 21 |

|                  |                                | from the enumeration "loss of communications."                                 | 22 |

|                  | NACK:                          | The remote system has not accepted the requested change to the allocated       | 23 |

|                  |                                | power. This value maps from the enumeration "non-acknowledge."                 | 24 |

|                  | ACK:                           | The remote system has accepted the requested change to the allocated power.    | 25 |

|                  |                                | This value maps from the enumeration "acknowledge."                            | 26 |

|                  | NULL:                          | There is no requested change to the allocated power. This value maps from the  | 27 |

|                  |                                | enumeration "not part of acknowledge cycle."                                   | 28 |

| removePowe       | er                             |                                                                                | 29 |

| Indica           | ates if the PS                 | SE is removing power from the PD by setting the PSE state diagram variable     | 30 |

| <del>pse_r</del> | eset to TRUE                   | due to a detected a loss of communications with the PD.                        | 31 |

| Value            | s: FALSE:                      | Power should not be removed from PD.                                           | 32 |

|                  | TRUE:                          | Power to be removed by PSE, pse_reset set to TRUE.                             | 33 |

|                  |                                |                                                                                | 34 |

|                  |                                |                                                                                |    |

A summary cross references between the DTE Power via MDI classification local and remote object class attributes and the PSE and PD power control state diagrams, including the direction of the mapping, is provided in Table 33–27.

| Object                       | Attribute                          | Mapping       | State diagram variable              |

|------------------------------|------------------------------------|---------------|-------------------------------------|

| oPSE managed<br>object class | aMirroredDLLPDRequestedPowerValue  | $\Leftarrow$  | MirroredPDRequested-<br>PowerValue  |

|                              | aDLLPSEAllocatedPowerValue         | $\Rightarrow$ | PSEAllocatedPower-<br>Value         |

|                              | aMirroredLostCommunication         | $\Rightarrow$ | loss_of_comms                       |

| oPD managed object class     | aDLLPDRequestedPowerValue          | $\Rightarrow$ | PDRequestedPower-<br>Value          |

|                              | aMirroredDLLPSEAllocatedPowerValue | ⇒             | MirroredPSEAllocat-<br>edPowerValue |

|                              | aLostCommunication                 | $\Leftarrow$  | loss_of_comms                       |

| 1           | 33.7.6.3 Timers                                                                                                                                              |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2           |                                                                                                                                                              |

| 3           | All timers operate in the manner described in 14.2.3.2 with the following addition. A timer is reset and stops                                               |

| 4           | counting upon entering a state where "stop x_timer" is asserted.                                                                                             |

| 5           |                                                                                                                                                              |

| 6           | pd_denial_timer                                                                                                                                              |

| 7           | A timer used to limit when a PD can make a new request to change the allocated power after a                                                                 |

| 8           | request is denied. The timer is done when it reaches 1 second.                                                                                               |

| 9           | pse_denial_timer                                                                                                                                             |

| 10<br>11    | A timer used to limit when a PSE can make a new request to change the allocated power after a request is denied. The timer is done when it reaches 1 second. |

| 12          | power_change_timer                                                                                                                                           |

| 13          | A timer that is started once a PSE reallocates the power for the PD. It may be used by the PSE sys-                                                          |

| 14          | tem.                                                                                                                                                         |

| 15          | 33.7.6.4 Functions                                                                                                                                           |

| 16          |                                                                                                                                                              |

| 17          | examine_request                                                                                                                                              |

| 18          | This function evaluates the request from the remote system to change the allocated power. This                                                               |

| 19          | function returns the following variables:                                                                                                                    |

| 20          | change_accept:                                                                                                                                               |

| 21          | Values: TRUE: The requested change to the allocated power is accepted                                                                                        |

| 22          | FALSE: The requested change to the allocated power is not accepted                                                                                           |

| 23          |                                                                                                                                                              |

| 24          |                                                                                                                                                              |

| 25          |                                                                                                                                                              |

| 26          |                                                                                                                                                              |

| 27          |                                                                                                                                                              |

| 28          |                                                                                                                                                              |

| 29          |                                                                                                                                                              |

| 30          |                                                                                                                                                              |

| 31          |                                                                                                                                                              |

| 32          |                                                                                                                                                              |

| 33          |                                                                                                                                                              |

| 34          |                                                                                                                                                              |

| 35          |                                                                                                                                                              |

| 36          |                                                                                                                                                              |

| 37          |                                                                                                                                                              |

| 38          |                                                                                                                                                              |

| 39          |                                                                                                                                                              |

| 40          |                                                                                                                                                              |

| 41          |                                                                                                                                                              |

| 42          |                                                                                                                                                              |

| 43          |                                                                                                                                                              |

| 44          |                                                                                                                                                              |

| 45          |                                                                                                                                                              |

| 46          |                                                                                                                                                              |

| 40<br>47    |                                                                                                                                                              |

| 48          |                                                                                                                                                              |

| 48<br>49    |                                                                                                                                                              |

| 49<br>50    |                                                                                                                                                              |

| 50<br>51    |                                                                                                                                                              |

| 51<br>52    |                                                                                                                                                              |

| 52<br>53    |                                                                                                                                                              |

| 55<br>54    |                                                                                                                                                              |

| J- <b>T</b> |                                                                                                                                                              |

### 33.7.6.5 State diagrams

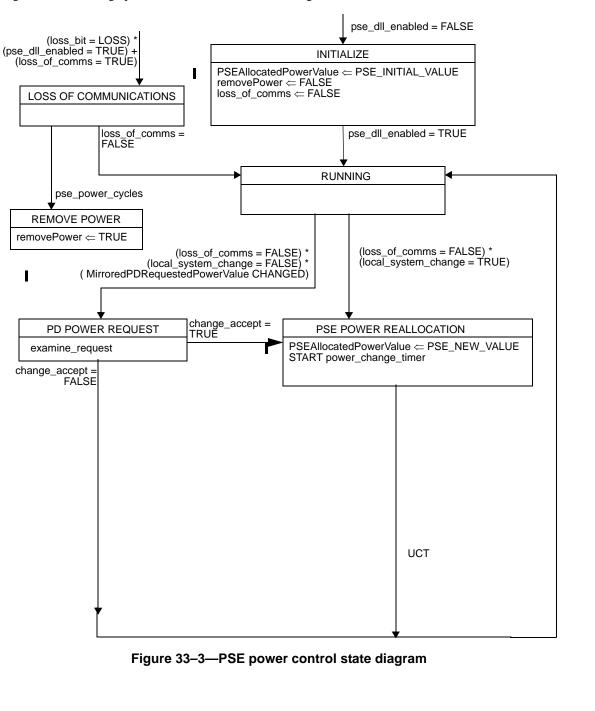

The general state change procedure for PSEs is shown in Figure 33–3.

The PSE responds to a PD's request or arbitrarily reallocates the PD's power classification through the aDLLPSEAllocatedPowerValue (30.9.1.1.18) attribute in the DTE Power via MDI classification PSE object

53

class. This appears to the PD as a change to the aMirroredDLLPSEAllocatedPowerValue (30.9.2.1.8) attribute in the DTE Power via MDI classification PD object class.

The state machines describe the behaviour above.

# 33.7.7.1 PSE State change procedure across a link

During normal operation the PSE machine is in the RUNNING state. If the PSE wants to initiate a change in the PD allocation, the local\_system\_change is asserted and the PSE enters the PSE POWER REALLOCA-TION state in the machine, which causes the PSEAllocatedPowerValue to be updated to the new level the PSE would like to assign indicated by the PSE\_NEW VALUE. The machine then returns to the RUNNING state.

If the PSE machine sees a change to the previously stored MirroredPDRequestedPowerValue, it recognizes a request by the PD to change its power allocation. The PSE examines the request by entering into the PD POWER REQUEST state. The PSE may decide to ignore the request, in which case it returns to the RUN-NING state or it may decide to change the PD allocation by entering the PSE POWER REALLOCATION state and behaves as described above.

When the PSE enters the PSE POWER REALLOCATION state it also re-starts a timer that may be used by the higher layer control function. For example, it may wait to see if the PD changes its request based on the reallocation. The use of the timer is outside the scope of this standard.

At any time, if the conditions of a loss of communication are met, the PSE enters the LOSS OF COMMUNI-CATIONS state.

# 33.7.7.2 PD State change procedure across a link

During normal operation the PD machine is in the RUNNING state. If the PD machine sees a change to the previously stored MirroredPSEAllocatedPowerValue, it recognizes a command by the PD to change its power allocation. Consequently, the PD enters the PSE POWER REALLOCATION state in the machine, which causes the PDRequestedPowerValue to also be updated to the new MirroredPSEAllocatedPower-Value. The machine then returns to the RUNNING state.

If the PD machine wants to initiate a request in its allocation, the local\_system\_change is asserted and the PD enters the PD POWER REQUEST state in the machine, which causes the PDRequestedAPowerValue to be updated to the new level the PD would like indicated by the PD\_NEW VALUE. The machine then returns to the RUNNING state.

At any time, if the conditions of a loss of communication are met, the PD enters the LOSS OF COMMUNI-CATIONS state.

If the local device is in the running state and the remote device changes to the request state, the local device observes the remote device's requested power through the aLLDPPoEPRemRequestedPDPowerValue (30.12.2.1.5) attribute in the DTE Power via MDI classification remote object class. The local device changes to an acknowledge state or a non-acknowledge state depending on acceptance of the remote device's requested change.

If the local device changes to the acknowledge state, it then changes the aLLDPPoEPLocActualPDPower-Value (30.12.1.1.9) attribute in the DTE Power via MDI classification local object class to match the remote device's requested power. The local device then sends a PDU reflecting its new settings.

If the local device is in the running state and it wishes to change to a new power mode, it may only do so if the remote device's most recent PDU reported that the remote device is in the running state. To change to a

new power mode, the local device sets its local requestedPower object and changes to the requesting state.

The local device then sends a PDU reflecting its requested power mode.

If the remote device changes to the acknowledge state in response to the mode change request from the local device, the local device updates its local actual power objects and changes to the running state. The local device then sends a PDU reflecting its new settings.

8 If the remote device changes to the non-acknowledge state in response to the mode change request from the

9 local device, the local device does not change its operating power mode and changes back to the running

10 state. The local device then sends a PDU reflecting its return to the running state.

In the event of a PDU collision (e.g., the local device is in a requesting state and the remote device changes to a requesting state), the local device does not change its operating power mode. The local device instead changes back to the running state and sends a PDU reflecting its return to the running state. If the local device is a PSE it may restart the request to change after pse\_denial\_timer, if the local device is a PD it may restart the request to change after pd\_denial\_timer (see 33.7.6.3).

18State definitions require that each request must be acknowledged or denied before returning to running state.19The requestor does not deassert the request until it receives an acknowledge or non-acknowledge. The part-20ner responds to a request as soon as it is seen. The requestor may persist or vacillate after a non-acknowl-21edge. To persist, it reasserts its request after a 1 second delay. It may decide to not persist.

# 33.7.8 Sample exchange

#### 33.8 Loss of management frame communication There are three scenarios which may cause a loss in management frame communication: Management frame communication not established after power-on, resulting in systems using 1) the power values established with Physical Layer classification Loss in management frame communication, resulting in systems reverting to last acknowl-2) edged Data Link Layer classification power value 3) Loss in management frame communication or communication not established after power-on, resulting in PSE optionally power cycling the PD after $2 \times TTL$ timeout value time period If Data Link Layer classification fails to come up within 5 minutes after the PSE has turned on power to the PD and the PSE identified the PD as a Type 2 PD via Physical Layer classification, the PSE may remove power. Upon loss of management frame communication, PSEs and PDs shall remain operational using the last acknowledged classification state. If a loss of management frame communication persists past the LLDP time to live (TTL) timeout value for the remote system (see IEEE Std 802.1AB-200X, subclause 9.5.4) plus an additional delay of $2 \times TTL$ time-out value for the remote system, a PSE may remove power, a PD shall update aLostCommunication (30.9.1.1.19) attribute in the DTE Power via MDI classification PD object class to the enumeration "loss of communications." The PSE may remove power at any time per Figure 33–1.

# 33.9 Protocol implementation conformance statement (PICS) proforma for Clause 33, DTE Power via MDI<sup>1</sup>

# 33.9.1 Introduction

The supplier of a protocol implementation that is claimed to conform to Clause 33, DTE Power via MDI, shall complete the following protocol implementation conformance statement (PICS) proforma.

A detailed description of the symbols used in the PICS proforma, along with instructions for completing the PICS proforma, can be found in Clause 21.