# Towards Consensus on 100GE CR/KR PCS&FEC&PMA Baseline

Yuchun Lu, Huawei Yan Zhuang, Huawei

IEEE 802.3 100 Gb/s, 200 Gb/s, and 400 Gb/s Electrical Interfaces Task Force

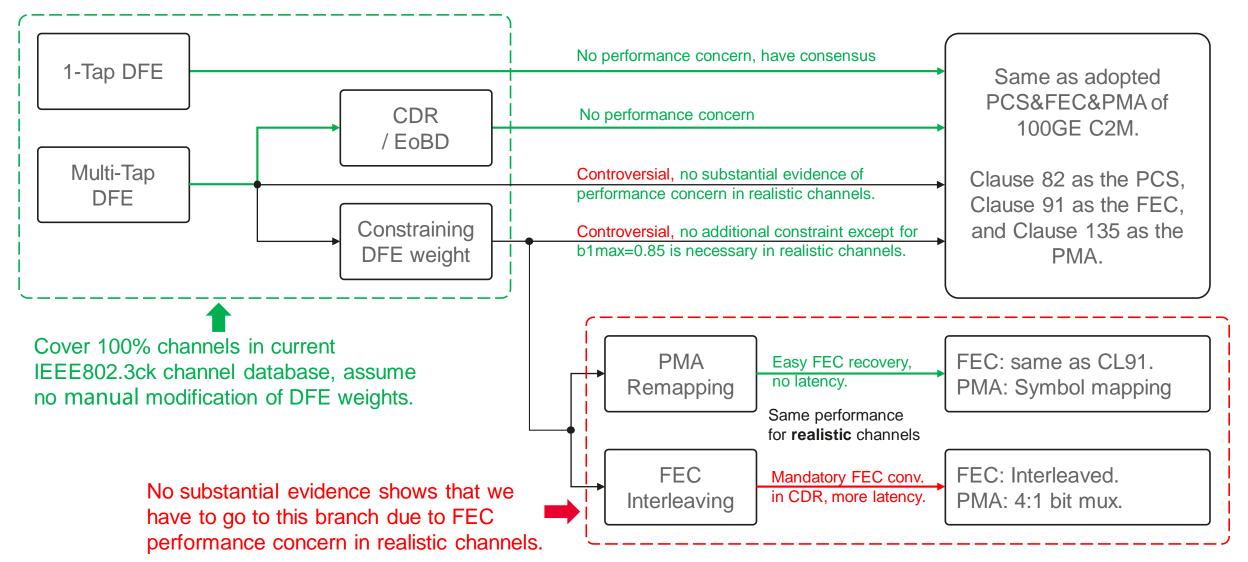

## Solutions for Multi-Tap DFE Error Propagation

| #                                              |         | PMD Solutions*                            |                                   |                                                                 | "PMA Remapping"                                                             | "Interleaved FEC"                                                                                                                   |                                                                     |

|------------------------------------------------|---------|-------------------------------------------|-----------------------------------|-----------------------------------------------------------------|-----------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|

|                                                |         | Constrain<br>DFE weight                   | EoBD<br>( <u>lu 3ck 01 0319</u> ) | CDR***                                                          | "PMA re-mapping" /<br>"4:1 symbol mux"<br>(lu_3ck_adhoc_01_041019)          | "2:1 bit mux"<br>(gustlin_3ck_01_0119)                                                                                              | "4:1 bit mux"<br>( <u>nicholl_3ck_adhoc_</u><br><u>01b_042419</u> ) |

| Performance                                    |         | ОК                                        | OK<br>(Best)                      | ок                                                              | OK?<br>(Same performance for <b>re</b> a                                    | alistic channels) OK<br>(Slightly worse)                                                                                            |                                                                     |

|                                                | Host IC | Negligible                                |                                   | 0                                                               | Negligible                                                                  | 1x 50G RS(544, 514) Encoder/Decoder.                                                                                                |                                                                     |

| Complexity<br>Increase                         | CDR     | 0                                         |                                   |                                                                 | <b>0</b><br>FEC decoders have already<br>been integrated inside CDR.        | Duplex FECL processing<br>2x 50G + 1x 100G RS(544, 514) Encoder<br>1x 50G RS(544, 514) Decoder.<br>All the functions are mandatory. |                                                                     |

| Latency<br>Increase                            | Host IC | 0                                         |                                   | 0                                                               | >50ns                                                                       |                                                                                                                                     |                                                                     |

|                                                | CDR     | 0                                         |                                   |                                                                 | <b>Ons w/o "FEC recovery" support;</b><br>~100ns w/ "FEC recovery" support. | >150ns 1 CDR;<br>>250ns 2 CDR.                                                                                                      |                                                                     |

| Protocol independent<br>"FEC recovery" support |         | No, Historical burden must be carried on. |                                   | <b>Yes,</b><br>FEC can be self-synchronized.                    | <b>No,</b><br>Has to process duplex FECL and do "FEC conversion".           |                                                                                                                                     |                                                                     |

| Define new Alignment Markers                   |         | No                                        |                                   | Νο                                                              | Yes                                                                         | No                                                                                                                                  |                                                                     |

| Standard Effort                                |         | None                                      |                                   | Minor **                                                        | A New Clause for "FEC conversion".                                          |                                                                                                                                     |                                                                     |

| Recommendation                                 |         | Preferred                                 |                                   | <b>Optional</b> , to support easy RS(544, 514) FEC termination. | Not                                                                         |                                                                                                                                     |                                                                     |

\* More PMD solutions are available. \*\* Optional PMA-remapping function within PMA Sublayer.

\*\*\* CDRs can be deployed on demand for PMD solution, but have to be mandatory for "Interleaved FEC" solution.

### Consensuses we already have

- No FEC performance concern for 1-tap DFE receiver, which is considered to be the mainstream receiver for 100GE CR/KR (<u>anslow\_3ck\_01\_0918</u> page 5).

- No FEC performance concern for most of channels with multi-tap DFE receiver. "Interleaved FEC" is dedicated for the "most difficult channels" (gustlin 3ck 01 0119 page 3), which have not been found yet! It will introduce more latency and mandatory FEC conversion inside CDR (lu 3ck adhoc 01 022719).

- **Precoding is essential** to guarantee the post-FEC performance due to the DFE based reference receiver (1-tap/multi-tap) (healey 100GEL 01 0318).

- Low cost solutions exist, they can address the FEC performance concern of multitap DFE receivers with negligible impacts on the system, including: constrain DFE weight, use CDR, EoBD\* as well as "PMA remapping"\*\*.

\* EoBD is Precoding 2.0 (<u>lu 3ck 01 0319</u>), which is also evaluated (<u>anslow 3ck adhoc 01 041019</u>). \*\* "PMA remapping" has same performance as "symbol-mux PMA" (<u>lu 3ck adhoc 01 041019</u>).

### Controversies

- Do we really have performance concern in realistic channels even with multi-tap DFE receivers?

- No evidence shows that there is FEC performance concern of multi-tap DFE receiver in realistic channels (without manual modification of DFE weights).

- "Constraint DFE weight" is a good idea. Currently, "b1max=0.85" is the only constrain that we might need. Any other channels need further constrain on the DFE weights?

- We have already have consensus on precoding, it does not make any sense to discuss post-FEC performance without consideration of precoding.

- It is conceptually wrong to discuss single FEC failure without talking about the failure probability. It is conceptually wrong to discuss the FEC performance out of the FEC working zone, e.g. at low Pre-FEC BER zone.

- Do we really need mandatory "Interleaved FEC" for 100GBASE-CR/KR? Any scenarios?

- We cannot find a proper scenario for mandatory "Interleaved FEC". The "most difficult channels" can be handled by adding CDR or other PMD solutions.

- "Interleaved FEC" is not the best in performance, but may be the most costly solution, although it may be a familiar one.

### Towards Consensus of 100GE CR/KR PCS&FEC&PMA

### Towards Consensus of 100GE CR/KR PCS&FEC&PMA

- Adopt Clause 82 as the PCS, Clause 91 as the FEC, and Clause 135 as the PMA for 100Gb/s Attachment Unit interface C2C (C2C-S&C2C-L) for this project. Same as C2M adopted in <u>gustlin 3ck 01 0319</u>.

- This already covers 100% channels in current IEEE 802.3ck channel database.

- This guarantee the interoperation with legacy modules without any cost.

- This guarantee the robustness of the end-to-end link.

- Don't obligate a costly feature (either in standard or implementation) only for minor channels which have not even been found. "PMD solutions" have no impact on the FEC decision.

- Leave other optional features open for further discussion. "Interleaved FEC" may be acceptable as an optional feature for C2C-L/KR, however its necessity proof is still missing and is highly recommended to be provided based on realistic channels.

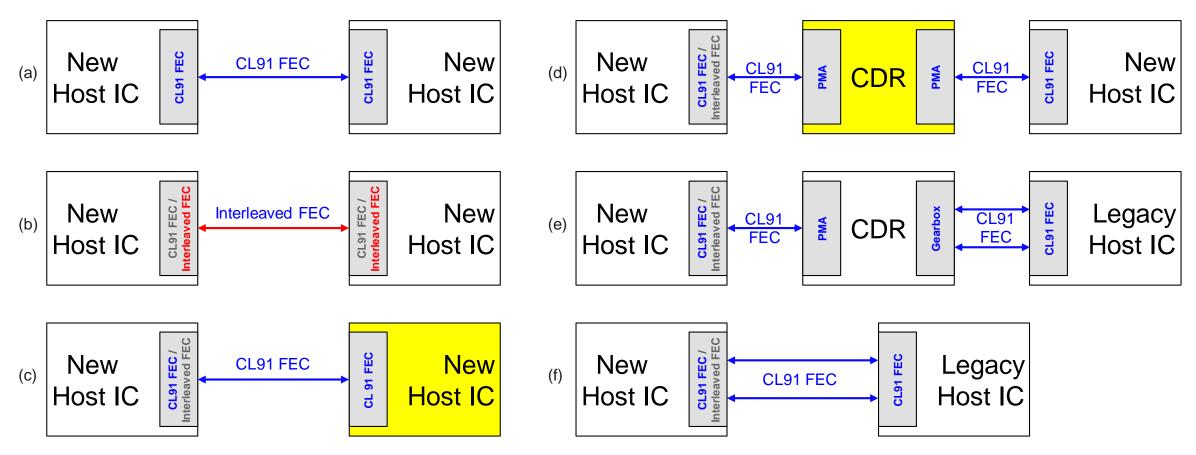

### Consideration on AN for dual mode FEC: Scenarios

- "CL91 FEC" has clear scenarios: (a), (c), (d~f); As long as there is "Legacy Host IC"/"CDR", we have to use "CL91 FEC".

- "Interleaved FEC" has only one scenario (b) however, it is still unclear without realistic "most difficult channel" been found.

- Assumption of "Implement both FECs" may lead to link failure due to auto-negotiation failure.

- Using "CL91 FEC" only introduces margin penalty of <0.5dB (<0.2dB in realistic channels), but the E2E link is still robust.

## **Necessity of CL91 FEC as Mandatory/default in AN**

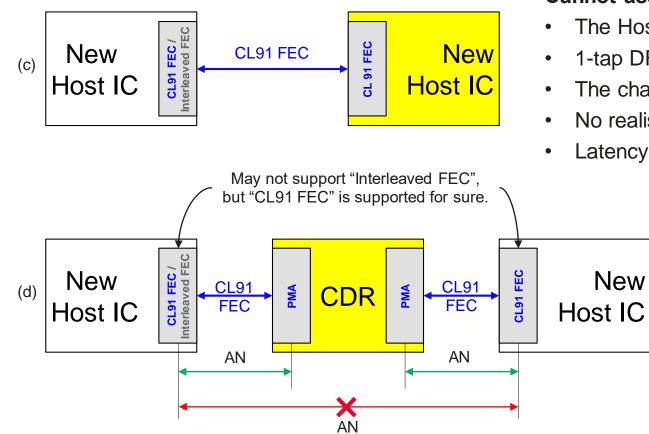

#### CDR may response to both sides to use "CL91 FEC".

- 1) This is not difficult channel, "interleaved FEC" is not necessary.

- 2) Both sides support "CL91 FEC" for sure without any ambiguity.

3) End-to-end link is robust.

### Cannot assume mandatory "Interleaved FEC" at Host IC.

- The Host IC may have stronger TX FFE.

- 1-tap DFE / Constraining DFE weights / EoBD can be used.

- The channels have large margin or use CDR for difficult channels.

- No realistic "most difficult channel" is found.

- Latency concern; Area and Power concern due to new fec.

### End-to-end auto-negotiation (AN) is complex, if CDR is used.

- Bit-transparent CDR is preferred. AN can only be done segment-by-segment.

- "Interleaved FEC" may not be supported by the "Host IC" on both side of CDR. "CL91 FEC" is supported without any doubt.

- Assumption of "Implement both FECs" may lead to **link failure** due to auto-negotiation failure.

- Using "CL91 FEC" only introduce margin penalty of <0.5dB (<0.2dB in realistic channels), but the E2E link is still robust.

### CL91 as mandatory FEC while AN for optional mode

- "Clause 91 FEC" should be "mandatory / default"

- All the chips (new/legacy) have to support it.

- "Interleaved FEC" may be "optional / non-default"

- Not all chips must support it. It is dedicated for 100GE CR/KR most difficult channels which have not been found yet!

- The behavior of AN operation with this option should be as follows to guarantee the end-to-end link robustness:

- ✓ For 100GBASE-KR and 100GBASE-CR PHYs CL91 operation is enabled as default.

- ✓ For 100GBASE-KR and 100GBASE-CR PHYs if either PHY requests "Clause 91" FEC then "Clause 91" operation is enabled.

- ✓ For 100GBASE-KR and 100GBASE-CR PHYs If both PHYs request "Interleaved FEC" then "Interleaved FEC" operation is enabled.

# Thank you !

### 把数字世界带入每个人、每个家庭、 每个组织,构建万物互联的智能世界。

Bring digital to every person, home, and organization for a fully connected, intelligent world.

### Reference

- FEC performance concern for 100GE-CR1/KR1 multi-tap DFEs with 4:1 bitmux PMA was shown in anslow 3ck 01 0918 with [0.7 0 0.2 0 0.2] channel. [0.7 0 0.2 0 0.2] is not a realistic channel and is too pessimistic, which is shown in <u>lu 3ck adhoc 01a 010219</u> and <u>lyubomirsky 3ck 01a 0319</u>.

- Interleaved FEC with 2:1 bit mux was proposed in <u>gustlin 3ck 01 1118</u>; Interleaved FEC with 4:1 bit mux was proposed in <u>nicholl 3ck adhoc 01b 042419</u>. In-depth analysis of interleaved FEC was given in <u>lu 3ck adhoc 01 022719</u>, which shown that Interleaved FEC will introduce more latency and complicated CDR, which is unnecessary and not affordable for some applications.

- PMD, PMA and FEC sublayer solutions for multi-tap DFE error propagation problem were analyzed in <u>lu 3ck 02 0319</u>. EoBD solution was discussed in <u>lu 3ck 01 0319</u>; PMA remapping was discussed in <u>lu 3ck adhoc 01 041019</u>. "PMA remapping" has the same performance as interleaved FEC with 2:1 bitmux PMA, and it can support "Protocol independent FEC recovery".

- Contributions that shown PMA remapping (symbol mux) and interleaved FEC with 2:1 bitmux has the same performance in realistic channels: <u>anslow 3ck 01 0119</u> page 12 &13, <u>anslow 3ck adhoc 01 041019</u>, <u>lyubomirsky 3ck 01a 0319</u>. <u>wu 3ck 01b 0319</u> shown that the equivalent DFE weight is smaller than 0.85, it can be verified by checking DFE weight database <u>sun 3ck 02a 0119</u>.

- EoBD (<u>lu 3ck 01 0319</u>) provides the best performance with negligible cost in latency and complexity <u>anslow 3ck adhoc 01 041019</u>.

- Two baseline options based on "PMD&PMA solutions" are provided in <u>zhuang 3ck 01 0519</u>.

- Dual FEC option is discussed in gustlin\_3ck\_adhoc\_01\_061219.