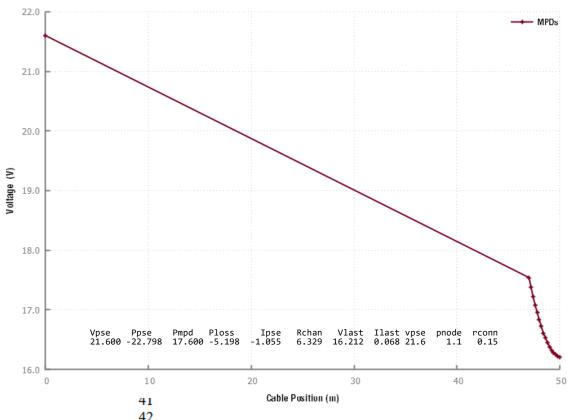

## Channel V / I / P / R Assumptions

Desire for industrial compatible supply voltages

Type 0 MPSE: 24V + / -20% = 21.6V to 26.4V

Desire to align power consumption with ODVA

PMPD TYPF0 = 1.1W

Requirement to reach 50m with 16 nodes

Assume 50m 20AWG cable @  $65C = 4\Omega$

Assume 20cm node separation

16 Nodes at end of mixing segment

Requirement to stay above 16V at last MPD

Table 189–1—System power types

|                         | 30V Max<br>MPSE<br>(Type 0) | 50V Max<br>MPSE<br>(Type 1) | Units |

|-------------------------|-----------------------------|-----------------------------|-------|

| V <sub>MPSE</sub> max   | 30                          | 50                          | V     |

| V <sub>MPSE</sub> min   | <del>26</del> 21.6          | 45                          | V     |

| V <sub>MPD</sub> min    | 16                          | 34                          | v     |

| I <sub>MPSE</sub> min   | <del>1000</del> 1100        | 1000                        | mA    |

| P <sub>MPSE</sub> min   | <del>-26</del> 23.76        | 45                          | w     |

| P <sub>MPD_1U</sub> max | <del>+-</del> 1.1           | 2                           | w     |

The last degree of freedom in solving the system is the resistance through each node

## **Existing Presentations on Connector Resistance**

Resistance through a node is made up of resistance due to connectors and resistance due to compensation

Connection resistance references:

https://ieee802.org/3/da/public/0724/Voss\_01\_da\_2024\_07\_10.pdf

https://ieee802.org/3/da/public/0124/boyer\_3da\_RevB\_01\_24\_24.pdf

Bob Voss's data suggests we need  $\sim 75 \text{m}\Omega$  allocated to connection resistance per node

$15m\Omega$  max resistance per connection (4 connections per node)

Add ~20% for temperature

Currently the specification allocates  $100m\Omega$  to loop resistance between TC1 and TC2

$75 \text{m}\Omega$  allocated to connectors

$25m\Omega$  left to allocate to 2 compensation elements (input / output elements)

$25m\Omega$  may be too low...

3

## **Compensation Elements**

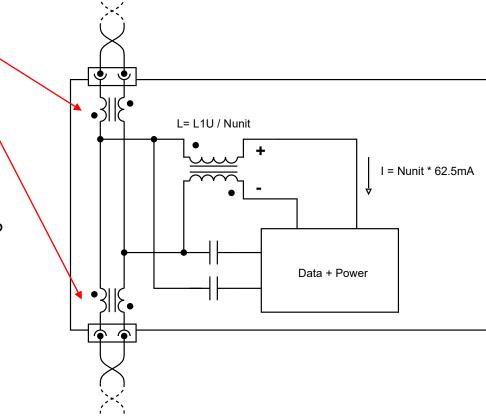

Low resistance / high current (>2A lsat) ~150nH coupled inductors are unique.

Not impossible to make, but not common yet

We need to set a target for vendors that pushes the limits, but does not push cost too hard

What is a good target resistance for these unique elements?

What is left in the budget after other parameters have been set?

## Power Budgeting for Type 0

Set other desirable parameters, then adjust DTE loop resistance until last node is above 16V

Table 189–1—System power types

|                         | 30V Max<br>MPSE<br>(Type 0) | 50V Max<br>MPSE<br>(Type 1) | Units |

|-------------------------|-----------------------------|-----------------------------|-------|

| V <sub>MPSE</sub> max   | 30                          | 50                          | v     |

| V <sub>MPSE</sub> min   | <del>26</del> 21.6          | 45                          | v     |

| V <sub>MPD</sub> min    | 16                          | 34                          | v     |

| I <sub>MPSE</sub> min   | <del>1000</del> 1100        | 1000                        | mA    |

| P <sub>MPSE</sub> min   | <del>-26-</del> 23.76       | 45                          | w     |

| P <sub>MPD_lU</sub> max | <del>+</del> 1.1            | 2                           | W     |

### Vmin = 21.6V, Pmpd = 1.1W, Rnode = 150mOhm, AWG20 @ 65C

44

45

46

48

### 189.2 Mixing segment

The mixing segment consists of cable, nodes, and terminations (see Figure 189-1). 100  $\Omega$  terminations are connected at the ends of the mixing segment and must be AC coupled. The DC loop resistance of the cable (excluding connectors and attached DTEs) shall be less than or equal to  $4 \Omega$ .

This resistance budget is based on supporting up to 17 in-line nodes (1 MPSE and 16 MPDs). Each DTE, including mated connectors and compensation components, adds up to  $100 \text{ m}\Omega$  to the loop resistance.

Edits Satisfy D2.1 Comments: 87, 88, 89, 90, 91

### Each DTE adds 150mΩ

Set resistance through each node to  $150 m\Omega$

Allocates ~75m $\Omega$  to connectors

Allocates  $\sim 75 m\Omega$  to compensators

Achieves other power deliver goals (Vmpse\_type0\_min, Pmpd\_type0, #Nodes, 50m Reach)

| 89.2 Mixing segment                                                                                                                                                                                                                                                                                         | 42             |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| The mixing segment consists of cable, nodes, and terminations (see Figure 189–1). 100 $\Omega$ terminations are connected at the ends of the mixing segment and must be AC coupled. The DC loop resistance of the cable excluding connectors and attached DTEs) shall be less than or equal to $4 \Omega$ . | 4:<br>4:<br>4: |

| This resistance budget is based on supporting up to 17 in-line nodes (1 MPSE and 16 MPDs). Each DTE, including mated connectors and compensation components, adds up to 100 mΩ to the loop resistance.                                                                                                      | 4°<br>4°<br>4° |

# MPSE / MPD Table Changes

Table 189–5—PSE output requirements

Replace w/ emdash

| Item | Parameter                                             | Symbol              | Unit | Min                                      | Max                   | Type | Additional<br>Information |

|------|-------------------------------------------------------|---------------------|------|------------------------------------------|-----------------------|------|---------------------------|

| 1    | DC output voltage<br>during POW-<br>ER_ON state       | $V_{	ext{MPSE}}$    | v    | <del>-26</del> 21.                       | 50                    | 0/1  |                           |

| 2    | Continuous output<br>capability in<br>POWER_ON state  | $P_{MPSE}$          | w    | <del>-26</del> -23.                      | 76 <del>-100</del>    | 0    | See 189.4.7               |

| 3    | Output slew rate dV/dt                                |                     | V/ms | -                                        | 9.5                   | ALL  |                           |

| 4    | Output current - at<br>short circuit condi-<br>tion   | $I_{LIM}$           | A    | <del>-1.1</del><br>1.2                   | <del>1.4</del><br>2.3 | ALL  | See 189.4.9               |

| 5    | Short-circuit time limit                              | $T_{LIM}$           | ms   | 50                                       | 75                    | ALL  | See 189.4.9               |

| 6    | Inrush time                                           | T <sub>Inrush</sub> | ms   | 10                                       | 20                    | ALL  |                           |

| 7    | MPD maintain<br>power signature<br>dropout time limit | T <sub>TPSDO</sub>  | ms   | 320                                      | 400                   | ALL  | See 189.4.10.1            |

| 8    | PD TPS time for validity                              | T <sub>TPS</sub>    | ms   | 6                                        | -                     | ALL  | See 189.4.10.1            |

| 9    | DC TPS current                                        | I <sub>HOLD</sub>   | mA   | 4                                        | 9                     | ALL  | See 189.4.10.1            |

| 10   | Error delay timing                                    | T <sub>ED</sub>     | ms   | 750                                      | -                     | ALL  |                           |

| 11   | Overload current                                      | $I_{CUT}$           | A    | P <sub>MPSE</sub> /<br>V <sub>MPSE</sub> | -                     | ALL  | See 189.4.8               |

| 12   | Overload time<br>limit                                | T <sub>CUT</sub>    | ms   | 50                                       | 70                    | ALL  | See 189.4.8               |

Table 189-9—MPD power supply limits

| Item | Parameter                       | Symbol                  | Unit | Min  | Max                   | Туре         | Additional<br>Information                     |

|------|---------------------------------|-------------------------|------|------|-----------------------|--------------|-----------------------------------------------|

| 1    | Input voltage                   | V <sub>Port_MPD</sub>   | v    | 16   | 30                    | 0            |                                               |

|      |                                 |                         |      | 34   | 50                    | 1            |                                               |

| 2    | Unit power                      | P <sub>MPD_1U</sub>     | W    |      | <del>1</del>          | 0 and<br>0/1 | 1 unit load                                   |

|      |                                 |                         |      |      | 2                     | 1            | 1 unit load                                   |

| 3    | Unit loading                    | N <sub>unit</sub>       | -    | 1    | 16                    | ALL          | See 189.5.5.3                                 |

| 4    | Input power                     | P <sub>MPD</sub>        | W    | 1.1  | <del>16</del><br>17.6 | 0 and<br>0/1 | N <sub>unit</sub> x P <sub>MP</sub> .<br>D_1U |

|      |                                 |                         |      | 2    | 32                    | 1            |                                               |

| 5    | Inrush current                  | I <sub>Inrush_MPD</sub> | mA   | -    | 10                    | ALL          | See 189.5.5.2                                 |

| 6    | MPD Type 0<br>Voltage threshold | V <sub>type0_th</sub>   | V    | 11.9 | 16                    | ALL          |                                               |

| 7    | MPD Type 1<br>Voltage threshold | V <sub>type1_th</sub>   | V    | 30.1 | 34                    | ALL          |                                               |

Edits Satisfy D2.1 Comments: 84, 93, 94, 95, 96, 97

7