# **The IEEE P802.3df Project – An Overview**

IEEE P802.3df Task Force IEEE 802.3 Jan 2022 Interim Session

John D'Ambrosia Acting Chair, IEEE P802.3df Task Force Futurewei, U.S. Subsidiary of Huawei

Mark Nowell Acting Vice Chair, IEEE P802.3df Task Force Cisco

# **IEEE P802.3 df Objectives**

#### Non-Rate Specific

- Support full-duplex operation only

- Preserve the Ethernet frame format utilizing the Ethernet MAC

- Preserve minimum and maximum FrameSize of current IEEE 802.3 standard

- Support a BER of better than or equal to 10 -13 at the MAC/PLS service interface (or the frame loss ratio equivalent)

- Provide support to enable mapping over OTN

#### • 200 Gb/s Related

- Support a MAC data rate of 200 Gb/s

- Support optional single-lane 200 Gb/s attachment unit interfaces for chip-to-module and chip-to-chip applications

- Define a physical layer specification that supports 200 Gb/s operation:

- over 1 pair of copper twin-axial cables in each direction with a reach of up to at least 1.0 meter

- over 1 pair of SMF with lengths up to at least 500 m

- over 1 pair of SMF with lengths up to at least 2 km

#### 400 Gb/s Related

- Support a MAC data rate of 400 Gb/s

- Support optional two-lane 400 Gb/s attachment unit interfaces for chip-to-module and chip-to-chip applications

- Define a physical layer specification that supports 400 Gb/s operation:

- over 2 pairs of copper twin-axial cables in each direction with a reach of up to at least 1.0 meter

- over 2 pairs of SMF with lengths up to at least 500 m

# **IEEE P802.3 df Objectives**

### • 800 Gb/s Related

- Support a MAC data rate of 800 Gb/s

- Support optional eight-lane 800 Gb/s attachment unit interfaces for chip-to-module and chip-to-chip applications

- Support optional four-lane 800 Gb/s attachment unit interfaces for chip-to-module and chip-to-chip applications

- Define a physical layer specification that supports 800 Gb/s operation:

- over 4 pairs of copper twin-axial cables in each direction with a reach of up to at least 1.0 meter

- over eight lanes of twin axial copper cables with a reach up to at least 2 meters

- over eight lanes over electrical backplanes supporting an insertion loss  $\leq$  28dB at 26.56GHz

- over 8 pairs of MMF with lengths up to at least 50 m

- over 8 pairs of MMF with lengths up to at least 100 m

- over 8 pairs of SMF with lengths up to at least 500 m

- over 8 pairs of SMF with lengths up to at least 2 km

- over 4 pairs of SMF with lengths up to at least 500 m

- over 4 pairs of SMF with lengths up to at least 2 km

- over 4 wavelengths over a single SMF in each direction with lengths up to at least 2 km

- over a single SMF in each direction with lengths up to at least 10 km

- over a single SMF in each direction with lengths up to at least 40 km

# **IEEE P802.3 df Objectives**

### • 1.6 Tb/s Related

- Support a MAC data rate of 1.6 Tb/s

- Support optional sixteen-lane 1.6 Tb/s attachment unit interfaces for chip-to-module and chip-to-chip applications

- Support optional eight-lane 1.6 Tb/s attachment unit interfaces for chip-to-module and chip-to-chip applications

- Define a physical layer specification that supports 1.6 Tb/s operation:

- over 8 pairs of copper twin-axial cables in each direction with a reach of up to at least 1.0 meter

- over 8 pairs of SMF with lengths up to at least 500 m

- over 8 pairs of SMF with lengths up to at least 2 km

### **Adopted Physical Layer Objectives**

### Technology Reuse

| Ethernet<br>Rate | Assumed<br>Signaling<br>Rate | AUI              | BP              | Cu Cable     | MMF<br>50m      | MMF<br>100m     | SMF<br>500m  | SMF<br>2km                                | SMF<br>10km                             | SMF<br>40km                             | Leverage existing or work-in-<br>progress 100 Gb/s per lane (e.g.<br>3cu, 3ck, 3db) to higher lane<br>counts |

|------------------|------------------------------|------------------|-----------------|--------------|-----------------|-----------------|--------------|-------------------------------------------|-----------------------------------------|-----------------------------------------|--------------------------------------------------------------------------------------------------------------|

| 200 Gb/s         | 200 Gb/s                     | Over 1<br>lane   |                 | Over 1 pair  |                 |                 | Over 1 Pair  | Over 1 Pair                               |                                         |                                         |                                                                                                              |

| 400 Gb/s         | 200 Gb/s                     | Over 2<br>Ianes  |                 | Over 2 pairs |                 |                 | Over 2 Pair  |                                           |                                         |                                         | Develop 200 Gb/s per lane electrical signaling for 1/2/4/8                                                   |

| 800 Gb/s         | 100 Gb/s                     | Over 8<br>Ianes  | Over 8<br>lanes | Over 8 pairs | Over 8<br>pairs | Over 8<br>pairs | Over 8 pairs | Over 8 pairs                              |                                         |                                         | lane variants of AUIs and<br>electrical PMDs                                                                 |

|                  | 200 Gb/s                     | Over 4<br>lanes  |                 | Over 4 pairs |                 |                 | Over 4 pairs | 1) Over 4 pairs<br>2) Over 4 $\lambda$ 's |                                         |                                         |                                                                                                              |

|                  |                              |                  |                 |              |                 |                 |              | 2) 0001 47.3                              |                                         |                                         | Develop 200 Gb/s per optical                                                                                 |

|                  | TBD                          |                  |                 |              |                 |                 |              |                                           | Over single<br>SMF in each<br>direction | Over single<br>SMF in each<br>direction | fiber for 1/2/4/8 fiber based<br>optical PMDs and 4 lambda WDM<br>optical PMD                                |

| 1.6 Tb/s         | 100 Gb/s                     | Over 16<br>lanes |                 |              |                 |                 |              |                                           |                                         |                                         |                                                                                                              |

|                  | 200 Gb/s                     | Over 8<br>Ianes  |                 | Over 8 pairs |                 |                 | Over 8 pairs | Over 8 pairs                              |                                         |                                         | Potential for either direct detect<br>and / or coherent signaling                                            |

|                  |                              |                  |                 |              |                 |                 |              |                                           |                                         |                                         | technology                                                                                                   |

### Making it all work together

11 Jan 2022 IEEE P802.3df Task Force, IEEE 802.3 Jan 2022 Electronic Interim Meeting

# **Technical Framing & Overview**

- At 18 Jan 2022 Meeting, further technical insight will be provided by Track Chairs –

- Architecture and Logic Overview, Gustlin

- Optical PMDs Overview, Nowell

- Electrical PMDs and AUIs Overview, Lusted

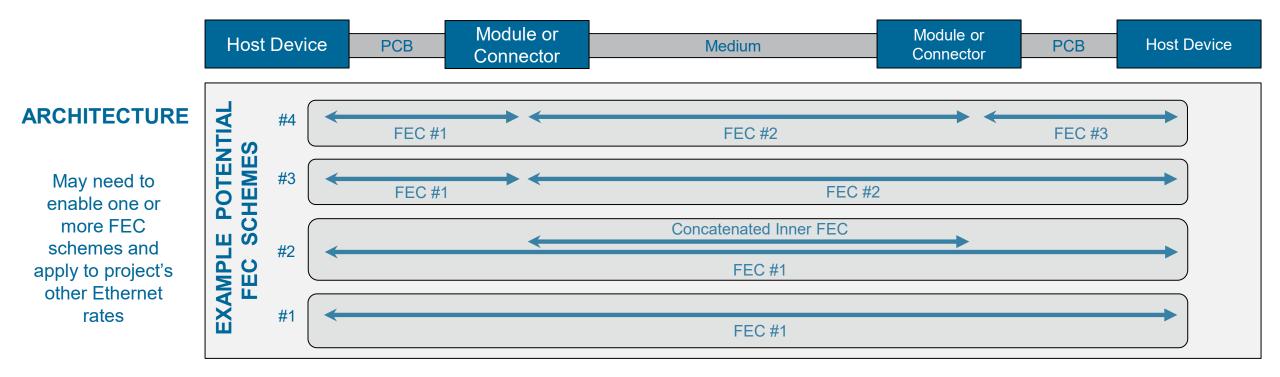

# **Development of Architecture & FEC Schemes**

# **Organization of Project Work**

| Logic                                                                                                                                                                                                                        | Electrical                                                                                                                                                                  | Optical                                                                               |  |  |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|--|--|--|--|--|

| <ul> <li>Amendments to MAC, RS,<br/>and MAC PHY interfaces</li> <li>RS and MII</li> <li>Extender Sublayers?</li> <li>PCS functions</li> <li>PMA functions</li> <li>Provide support to enable<br/>mapping over OTN</li> </ul> | <ul> <li>Extender Sublayer?</li> <li>C2C AUIs</li> <li>C2M AUIs</li> <li>Copper PMDs</li> <li>Channel characteristics for<br/>electrical interfaces and<br/>PMDs</li> </ul> | <ul> <li>Optical PMDs</li> <li>MDIs?</li> <li>Media Characteristics</li> </ul>        |  |  |  |  |  |

| FEC Architecture and Budget                                                                                                                                                                                                  |                                                                                                                                                                             |                                                                                       |  |  |  |  |  |

| Overall Architecture                                                                                                                                                                                                         | <ul> <li>FEC related to electrical<br/>interfaces and PMDs</li> </ul>                                                                                                       | <ul> <li>FEC related to Optical<br/>PMDs</li> </ul>                                   |  |  |  |  |  |

| <ul> <li>Management related to<br/>Logic functions (Clauses<br/>30, 45, etc.)</li> </ul>                                                                                                                                     | <ul> <li>Management related to<br/>electrical interfaces and<br/>PMDs (Clauses 30, 45,<br/>etc.)</li> </ul>                                                                 | <ul> <li>Management related to<br/>Optical PMDs (Clauses 30,<br/>45, etc.)</li> </ul> |  |  |  |  |  |

Further insight to be provided by Track Leadership @ 18 Jan 2022 Meeting

11 Jan 2022 IEEE P802.3df Task Force, IEEE 802.3 Jan 2022 Electronic Interim Meeting

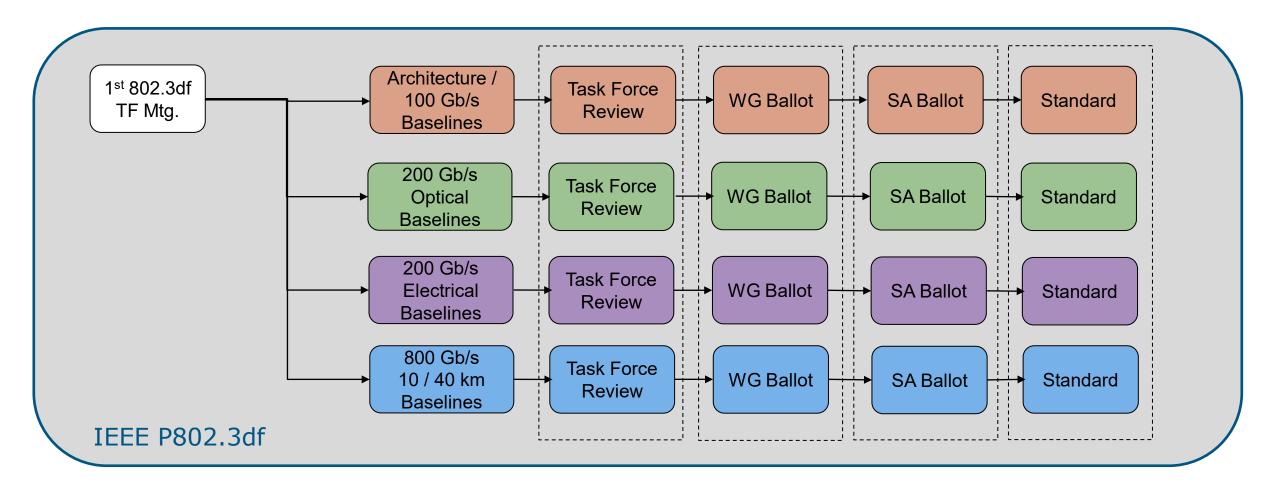

## **Project Flow – Ideal Circumstances**

### Under "ideal circumstances" the various technology branches will align.

11 Jan 2022 IEEE P802.3df Task Force, IEEE 802.3 Jan 2022 Electronic Interim Meeting

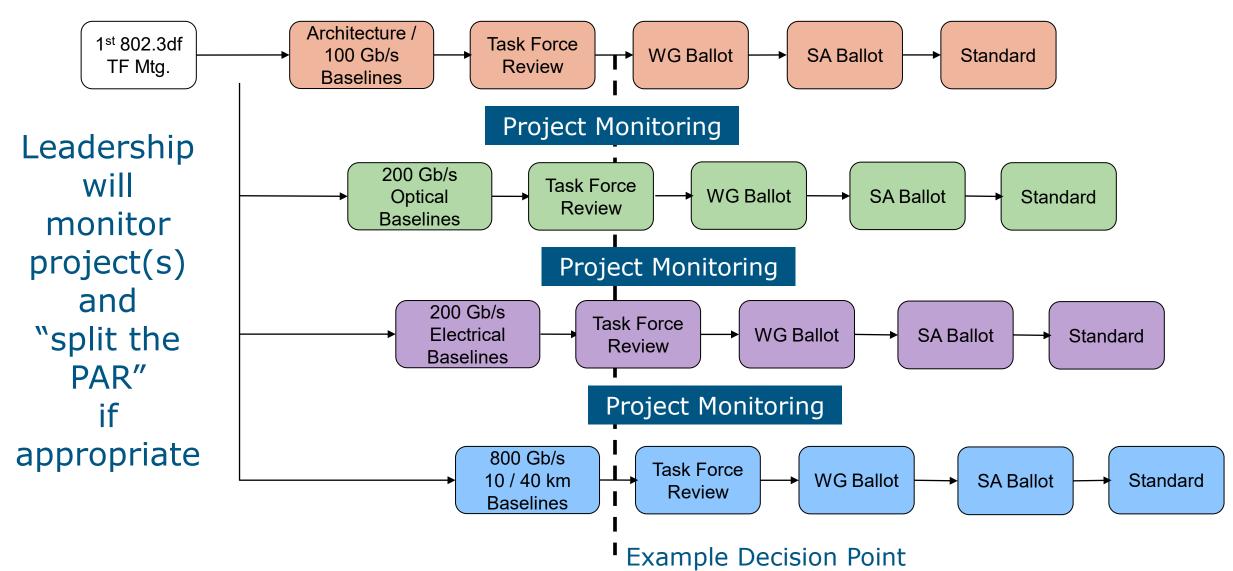

## **Project Flow – Potential Reality**

### **Moving Forward**

□ The development of the overall architecture is key.

- Timelines for different technology branches are unknown at this point, but TF leadership will monitor to progress the project.

- □ "Splitting the PAR" is a known process in IEEE 802

- □ PER IEEE 802 Operations Manual, Section 9.2 IEEE 802 LMSC approval

At the discretion of the IEEE 802 LMSC Chair, PARs for ordinary items (e.g., Maintenance PARs) and PAR changes essential to the orderly conduct of business (e.g., <u>division of</u> <u>existing work items</u> or name changes to harmonize with equivalent ISO JTC-1 work items) may be placed on the IEEE 802 LMSC agenda if delivered to IEEE 802 LMSC members 48 hours in advance