# IEEE P802.3df Electrical PMDs and AUIs Overview

Kent Lusted, Intel Corporation

#### Agenda

- Review

- 100 Gbps/lane Signaling

- 200 Gbps/lane Signaling

- AUIs

- Copper cables

- Other

This is not an exhaustive summary. We are a contribution-led group.

#### **Presentation Focus**

|   | Logic                                                                                                                                                | Electrical                                                                                                                                                          | Optical                                                                               |

|---|------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|

| • | Amendments to MAC, RS,<br>and MAC PHY interfaces<br>RS and MII<br>Extender Sublayers?<br>PCS functions<br>PMA functions<br>Provide support to enable | <ul> <li>Extender Sublayer?</li> <li>C2C AUIs</li> <li>C2M AUIs</li> <li>Copper PMDs</li> <li>Channel characteristics for electrical interfaces and PMDs</li> </ul> | <ul> <li>Optical PMDs</li> <li>MDIs?</li> <li>Media Characteristics</li> </ul>        |

|   | mapping over OTN                                                                                                                                     |                                                                                                                                                                     |                                                                                       |

| F | EC Architecture and Budge                                                                                                                            | et                                                                                                                                                                  |                                                                                       |

| • | Overall Architecture                                                                                                                                 | <ul> <li>FEC related to electrical<br/>interfaces and PMDs</li> </ul>                                                                                               | <ul> <li>FEC related to Optical<br/>PMDs</li> </ul>                                   |

| • | Management related to<br>Logic functions (Clauses<br>30, 45, etc.)                                                                                   | <ul> <li>Management related to<br/>electrical interfaces and<br/>PMDs (Clauses 30, 45,<br/>etc.)</li> </ul>                                                         | <ul> <li>Management related to<br/>Optical PMDs (Clauses 30,<br/>45, etc.)</li> </ul> |

https://www.ieee802.org/3/df/public/22 01/dambrosia 3df 01 220111.pdf

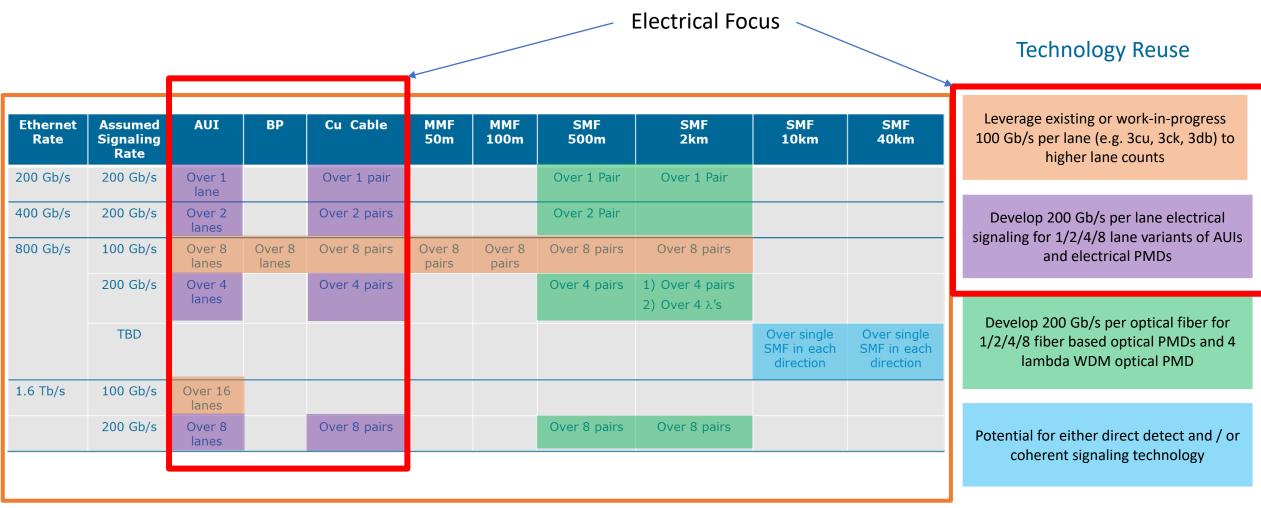

#### **Adopted Physical Layer Objectives**

#### Making it all work together

https://www.ieee802.org/3/B400G/public/21\_1028/B400G\_overview\_c\_211028.pdf

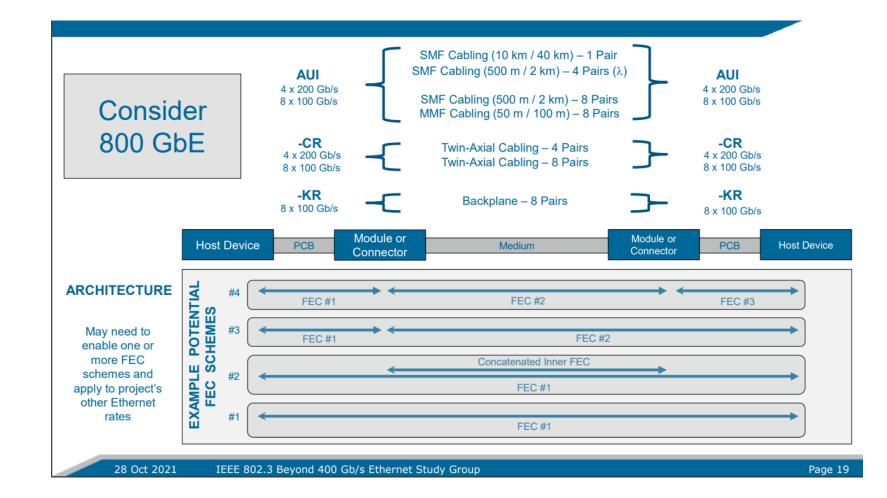

#### FEC Schemes and Electrical Dependencies

Electrical interface and PMD parameters will vary widely across the media types and FEC schemes

# 100 Gbps/lane Signaling

#### Key Assumptions

- #1. No <u>significant</u> architecture, form factor, parametric or use case changes when compared to 3ck electrical interfaces and PMDs

- Supporting a 200 Gbps/lane FEC structure on 100 Gbps/lane electrical interfaces could impact signaling rate

## 800GbE (8x100) Strategy

- Monitor progress of 3ck through SA ballot cycle

- Expand 3ck interfaces and PMDs for lane widths up to 8

- AUI C2M

- AUI C2C

- Copper cable

- Backplane

- Adopt/modify MDI, PMD form factors as required

- Update COM reference receiver and transmitter parameters, if needed

## 1.6TbE (16x100) Strategy

- Expand 3ck interfaces for lane widths up to 16

- AUI C2M

- AUI C2C

- Update COM reference receiver and transmitter parameters, if needed

- Adapt this plan if new PMDs surface

# 200 Gbps/lane Signaling

#### Key Assumptions

- #1. Broad engagement in developing 200 Gbps/lane electrical interfaces and PMDs is impacted by work within 3ck

- #2. PMD/AUI parameters affect FEC architecture, pre FEC BER target, FEC gain requirements, etc.

- Balance power, complexity, cost, latency and encoded lane rates

- Segmented and concatenated FEC schemes could require different bit rates

- #3. Electrical interfaces (e.g AUIs) might use a different FEC strategy than the electrical PMDs

#### 200 Gbps/lane

#### AUIs (Nx200)

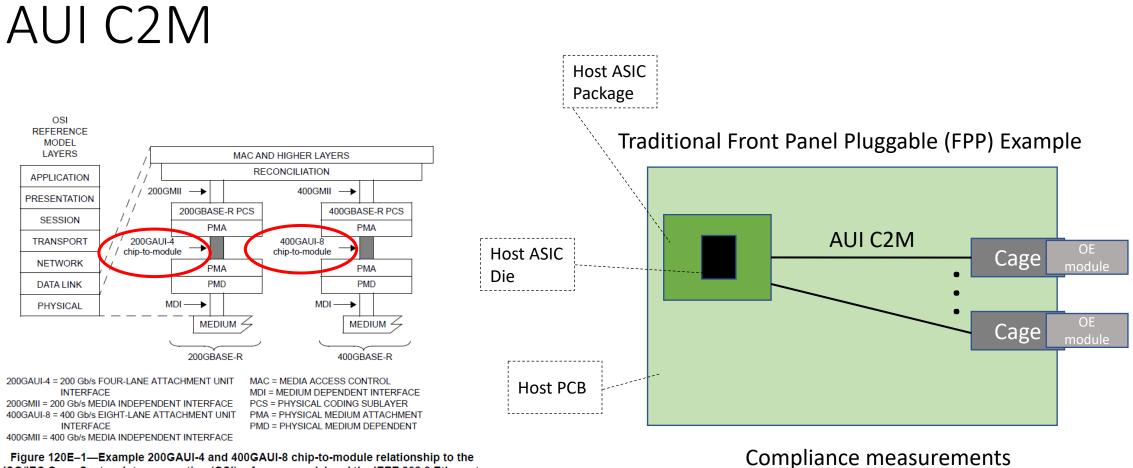

- Chip-to-module (C2M) and chip-to-chip (C2C) AUI objectives exist today to address the "traditional" front panel pluggable use case

- What is the desired physical reach and IL for front panel pluggable (FPP) AUI C2M?

- Is it compatible with the copper cable PMD?

- Electrical modulation choice codependent upon optics

- Optional TX precoder?

- Error statistics

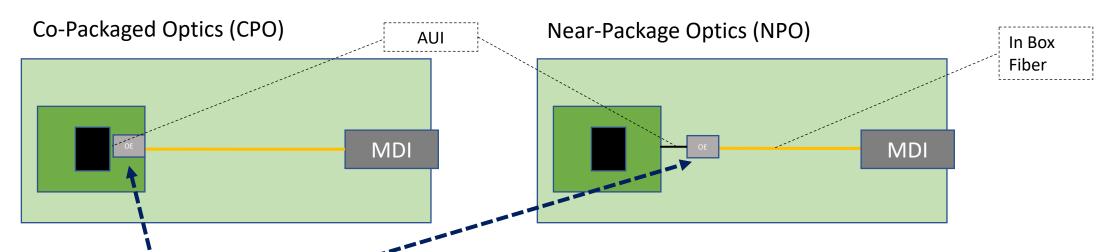

## New Use Cases Emerging: CPO, NPO

- Co-packaged/Near-Package optics may have fixed (soldered) and pluggable (e.g. socketed) instantiations

- If possible, map these instantiations to the "traditional" AUI C2C and C2M compliance test models for maximum commonality

- Is there a need for specialized AUI variants for CPO and NPO?

#### More on AUIs

- Will module and host VEC/EH be sufficient or is a new method needed?

- Existing VEC/EH methods appear to be strained at 3ck (100 Gbps/lane) rates

- Expand the number of module-to-host electrical output modes?

- Or move to link\_training-like process?

- Is there a market need for multiple-rates-per-lane?

- Need channel contributions to determine host and module equalization demands!

## Copper Cable (Nx200)

- Modulation selection (PAM4 vs. PAM6) will be challenging

- Both choices have merits and impacts

- Optional TX precoder?

- What is the desired physical reach and IL for copper cable hosts?

- Is it compatible with FPP AUI C2M, CPO, NPO?

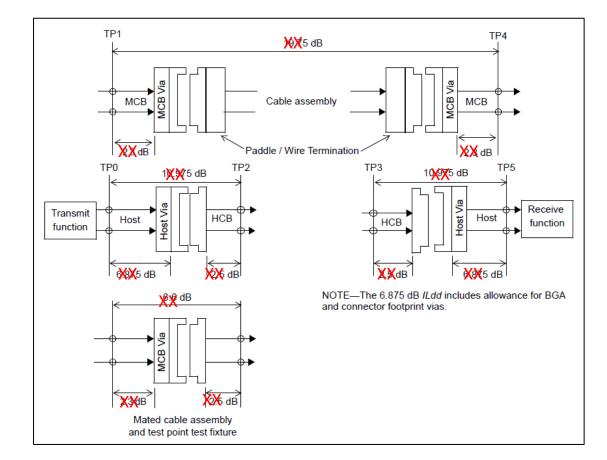

- Revisit test fixtures (HCB, MCB, etc.) and methods

- Is there continued interest in specifying active copper cable types?

- Fully retimed, half retimed, linear only?

- Error statistics

- Need channel contributions to determine equalization demands!

#### Reference Transmitter and Receiver

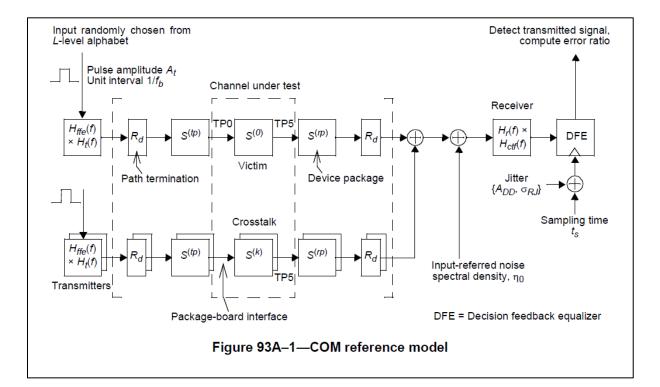

- COM used extensively for electrical interfaces and PMDs

- Channel characterization and calibration

- Receiver testing

- Update the DFE-based ref RX and TX

- Is it still good enough?

- Significant effort required if a new FOM or model is selected

#### Other

- Investigate host device package model parameters

- Assess optical module package impacts for FPP, CPO, NPO cases

- Auto-Negotiation and Link Training

- AN73 link codeword base page is out of space

- Link Training extensions for more/new parameters

- What is an acceptable value for link\_fail\_inhibit\_timer?

- Backplane objective(s) & CSD supporting material?

- Including reach/IL targets

- Control and management interface

#### Summary

- 100 Gbps/lane contributions needed

- Baseline proposal thoughts for AUIs, BP, Cu cable, MDIs, etc.

- Initial 200 Gbps/lane contributions focus areas:

- Host physical design/architecture

- Use cases: FPP, CPO, NPO, combo AUI/CR port, Cu cable

- "First order" channel contributions for equalization studies

## Thanks!

ISO/IEC Open System Interconnection (OSI) reference model and the IEEE 802.3 Ethernet model

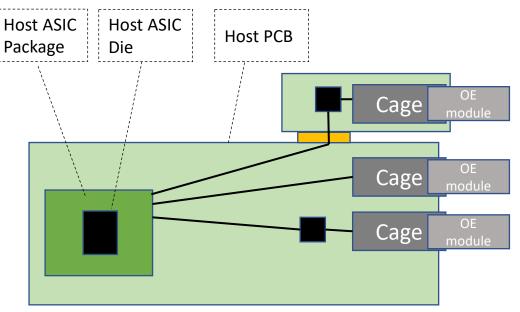

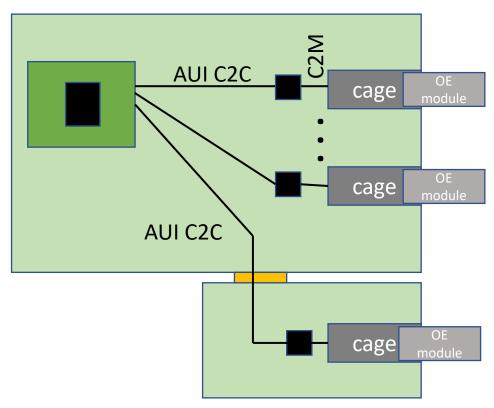

Figure above is an example architectural diagram of existing chip-to-module electrical interfaces and is not intended to represent the direction this group must take. Compliance measurements are done at a separable connector

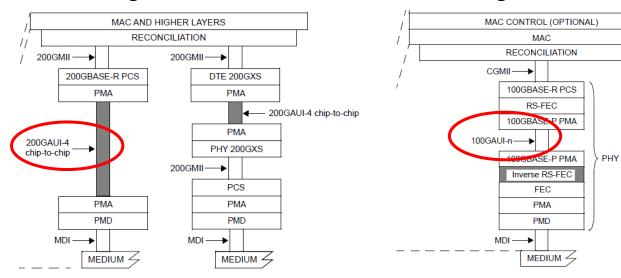

#### AUI C2C

#### Annex 120D: Figure 120D-1

Clause 152: Figure 152-1

#### Traditional Examples

Figure above is an example architectural diagram of existing chip-to-module electrical interfaces and is not intended to represent the direction this group must take.