# 200G/lane Electrical interfaces – System implications

Adee Ran, Cisco

Liav Ben-Artsi, Marvell

### Supporters

- Upen Reddy Kareti, Cisco

- Itamar Levin, Intel

## This presentation is about...

Adopted Physical Layer Objectives & Nomenclature And that Ethernet Assumed AUI BP Cu Cable MMF MMF SMF SMF SMF SMF 50m 100m 500m 2km 10km Rate Signaling 40km Rate 200 Gb/s 00 Gb/s Over 1 lane Over 1 pair Over 1 Pair Over 1 Pair 200GAUI-1 200GBASE-CR1 TBD TBD 400 Gb/s 100 Gb/5 Over 4 Pair TRD 200 Gb/s Over 2 lanes Over 2 pairs Over 2 Pair 400GAUI-2 400GBASE-CR2 TBD 800 Gb/s 100 Gb/s Over 8 lanes Over 8 lanes Over 8 pairs 800GBASE-KR8 800GAUI-8 800GBASE-CR8 800GBASE-VR8 800GBASE-SR8 TBD 200 Gb/s Over 4 pairs 1) Over 4 pairs Over 4 lanes Over 4 pairs 800GAUI-4 800GBASE-CR4 TBD TBD Over 4 λ's TBD Over single Over single SMF in each SMF in each direction direction TBD TBD 1.6 Tb/s 100 Gb/s Over 16 lanes 1.6TAUI-16 200 Gb/s Over 8 lanes Over 8 pairs Over 8 pairs Over 8 pairs 1.6TAUI-8 1.6TBASE-CR8 TBD TBD We need to approach all of this holistically 23 Maril 20022 IEEE P802.3df Task Force, Architecture and Logic Ad hoc Page 3

Source: dambrosia 3df logic 220411a

### Outline

- AUI C2M endpoints

- The ToR switch use case

- Loss budget

- Architecture implications

- Call for action

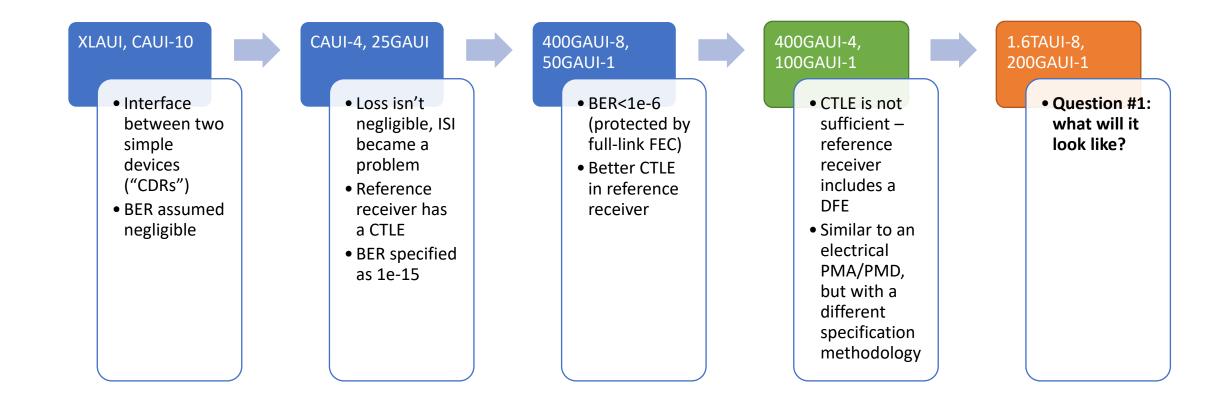

### Evolution of C2M AUI endpoints

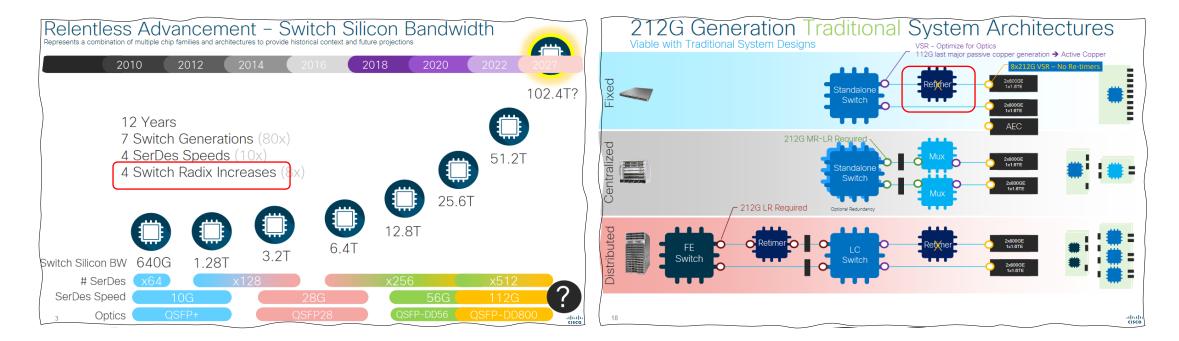

## Switch applications

Source: chopra b400g 01 210208 (slides 3 and 18)

### Additional switch use cases

- There are other switch architectures

- Co-packaged optics (CPO)

- Near-package optics (NPO)

- Not the scope of this presentation.

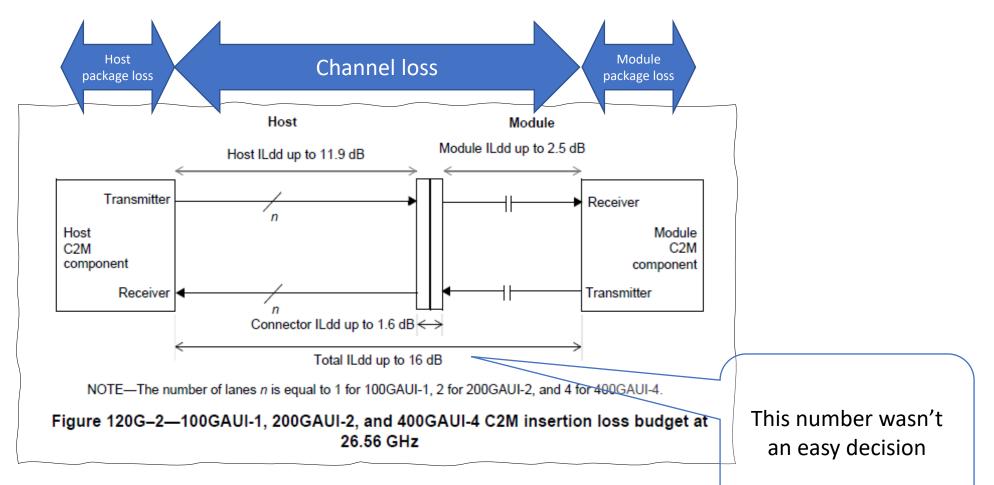

### C2M elements (from 802.3ck)

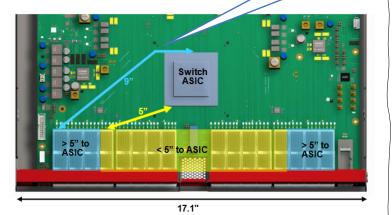

### ToR switch geometry

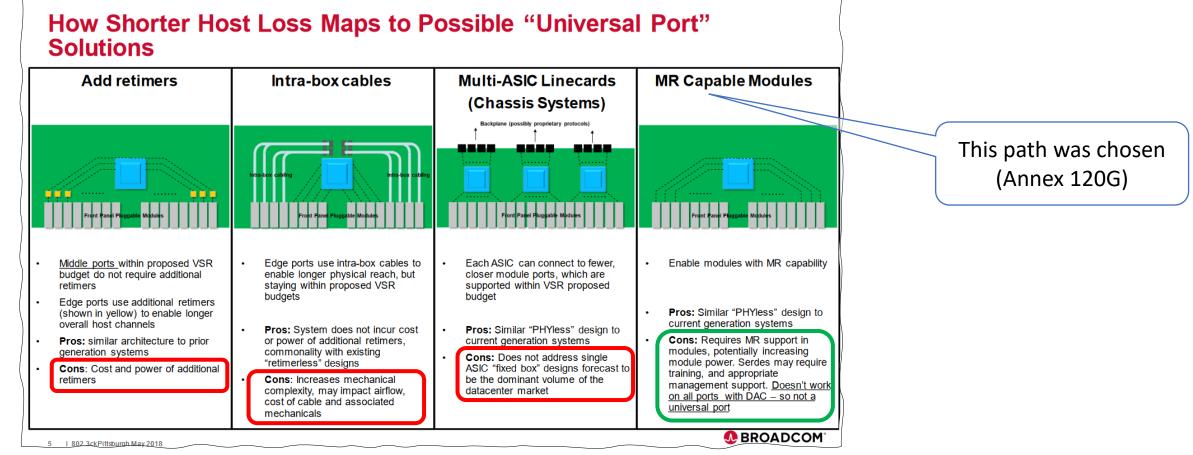

#### Architectural changes to ToRs due to reduced physical VSR reach

- Hypothetical Example:

- 25.6T, 256 x 100G

- 1RU box, Single ASIC (ToR design profile, also used as virtual chassis, aka "Fixed Box")

- Can be used with all optical IO in a spine application (common practice today in hyperscale datacenters)

- 32 x 800G module cages, all front panel IO

- Using Rosemont budget proposal from Jane Lim:

- <u>http://www.ieee802.org/3/100GEL/public/18\_03/lim\_100GEL\_01b\_0318.pdf</u>

- [~ 5" Host trace supported for VSR channels]

- Approximately 12 / 32 module cages cannot accommodate the proposed host budgets (VSR or CR), requiring either intermediate retimers, or intra-box cabling

from switch package to connector pads + Large switch ASIC package

9" (lower bound)

This application influenced the Annex 120G specifications, which assume a ball-to-ball IL of **16 dB** @ 26.56 GHz.

Assuming PAM4: ~32 dB @ 53 GHz?

#### Source: stone 3ck 01a 0518

+ 802.3ckPittsburgh May 2018

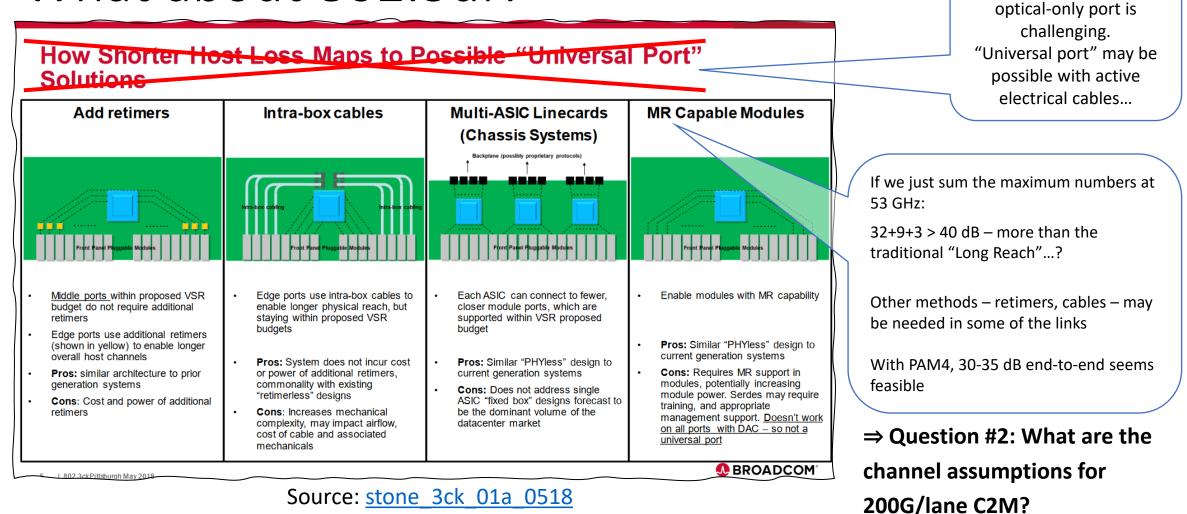

### Other options discussed in 802.3ck

#### Source: stone 3ck 01a 0518

### Package considerations

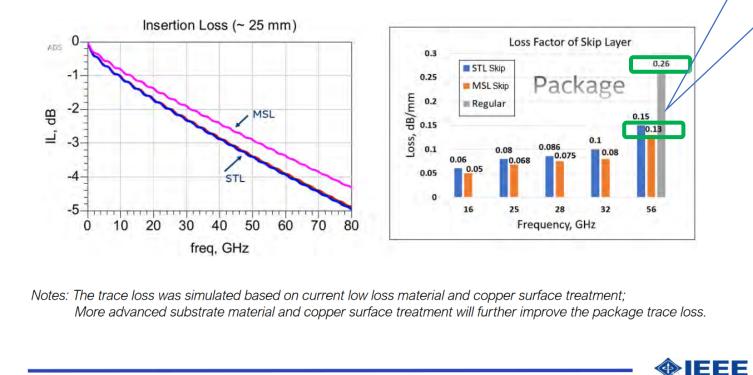

### Package Skip Layer Trace Loss

Mar 2022

Source: mli 3df 01 220316

There are ways to reduce package trace loss to perhaps 0.13 dB/mm

#### But...

High-radix switch packages can't use skip layer and microstrips in all lanes.

These methods are typically used in the longer traces (e.g. 40 mm) to make them "look like" the reference package...

The 802.3ck COM reference package is based on "regular" trace of 31 mm

31\*0.26 ≈8 dB @ 53 GHz +~1 dB core via ⇒ 9 dB allocation for switch package? 1-3 dB for module package?

P802.3df

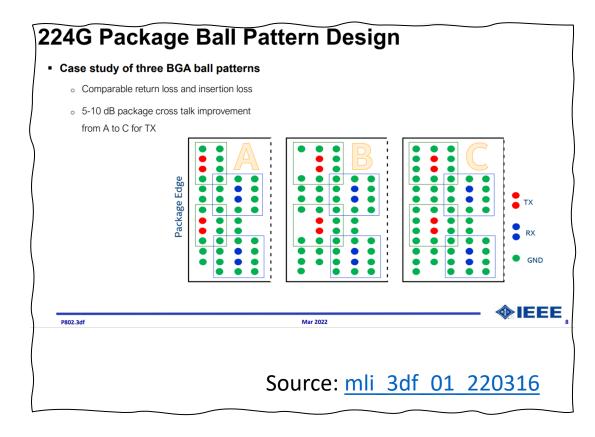

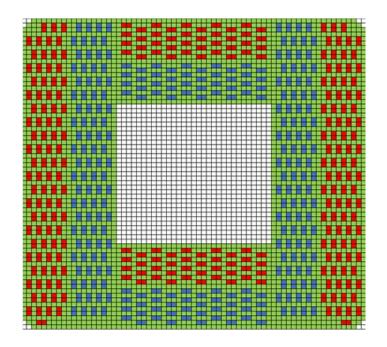

## Ball pattern of a high-speed radix switch

**Thought exercise:**

Assume the minimum presented Tx/Rx separation, populate 256 lanes...

Just the AUI signals require a 69x69 grid (in practice, more are needed)

$\Rightarrow$  larger package than previously assumed (>75 mm square?)

$\Rightarrow$  longer traces

## Host package and PCB recommendations

### 224G PAM4 Package Design Summary(slide 26)

- Desired next generation package trace loss target for interpretation flexibility: 0.1 dB/mm at Nyquist frequency

- $\circ~$  Skip-layer trace routing is required for mitigating the transmission loss

- o Low loss material and advanced copper surface treatment are required

- 0.8mm ball pitch is recommended (0.65mm or smaller preferred)

- Smaller ball size can further reduce discontinuities and package loss

- BGA ball pattern needs to be PCB breakout friendly and fully shielded

- Ground stitching via pitch < 1/10 wavelength along TX/RX traces and < 1/4 wavelength everywhere else in the vicinity of the 224G channel routing are required

### 224G PAM4 PCB Design Summary

- Desired next generation PCB trace loss target for interpretation flexibility: 1 dB/inch at Nyquist frequency

- Skip-layer trace routing is required

- o Ultra low loss material is required

- HVLP copper surface treatment is required

- PCB via stub length < 8mil is required</p>

- Well controlled process variation of Dk, Df and dielectric thickness is required

With the density required for highradix switch ASIC package and PCBs, these design recommendations may not always be met

Source: mli 3df 01 220316

(slide 27)

### What about 802.3df?

At 200G/lane even an

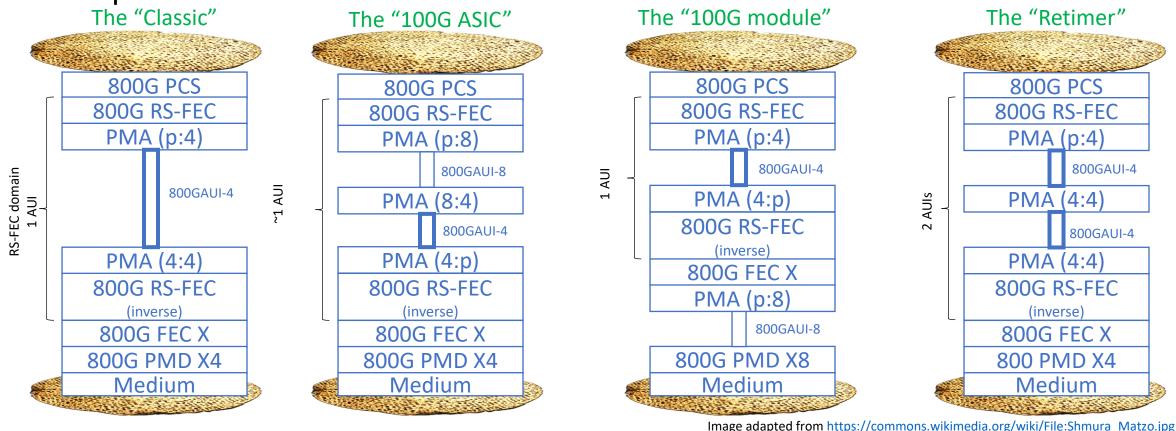

### FEC architecture implications

• Achieving BER<<1e-4 with 200G/lane AUI isn't a safe assumption.

- As mentioned in <u>rabinovich 3df 01a 220224</u>, even a relatively "easy" channel does not reach that goal. More so with switch AUI of 30-35 dB.

- Assuming the RS(544,514) (KP FEC) for the AUI FEC, as suggested in <u>gustlin 3df logic 220411</u>, its full correction capability will likely be required for one end of the link.

- As it seems:

| End-to-end                                                                                              | ×            |

|---------------------------------------------------------------------------------------------------------|--------------|

| Encapsulated with "imperfect" outer (optical) FEC (inner end-to-end FEC corrects some "optical" errors) | ×            |

| Encapsulated with "perfect" outer (optical) FEC, inner end-to-end FEC protects AUIs on both ends        | 6            |

| Segmented                                                                                               | $\checkmark$ |

## Architecture/Holistic approach

- As stated in <u>dambrosia</u> <u>3df</u> <u>logic</u> <u>220411a</u>, we should also consider cases with more than one AUI on one or both sides.</u>

- Our options are:

### Implication of segmented FEC

- Frame loss is a result of uncorrectable codewords on either of the FEC segments

- These events are independent of each other, so easy to analyze and monitor

- Uncorrectable codeword ratio (UCR) of FEC-protected AUIs should be allocated from the total budget

- From the UCR of the FEC-protected AUIs, we can calculate the maximum pre-FEC BER as we had in previous projects

- More than one AUI can be in one FEC domain

- For now, assume the pre-FEC BER is 5e-5 to support two AUIs

- Given maximum BER and channel assumptions, we can start analyzing reference Tx and Rx parameters...

- So we need to define our channel assumptions!

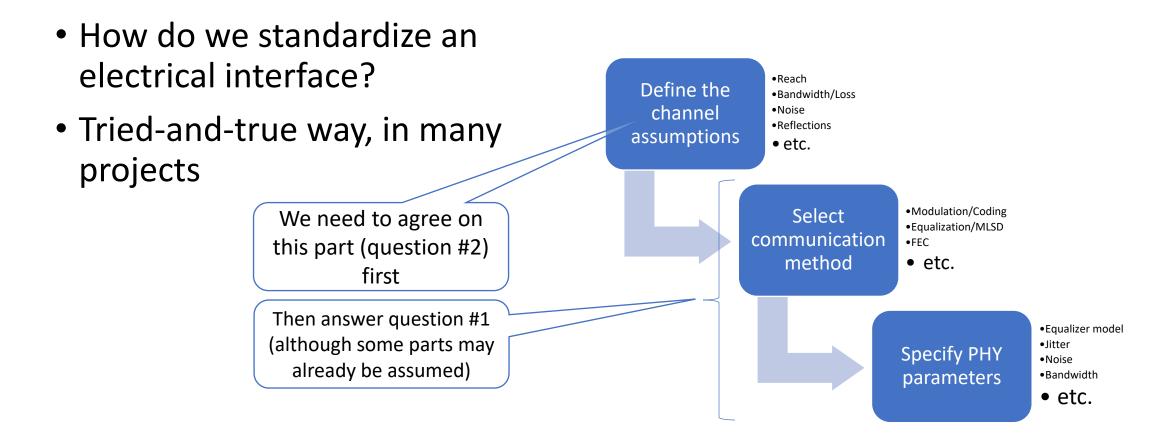

### Thoughts about our process

# Partial answer to question #1

(200G/lane AUI endpoints)

- Authors' opinion:

- At least as complex as reference Rx/Tx of 100G electrical PMDs

- Including, e.g., a strong equalizer

- BER similar or slightly better than 100G electrical PMDs

- Assuming segmented FEC architecture with KP FEC

- Every AUI segment must be protected by FEC; FEC domain (between encoding and decoding) spans at most two adjacent 200G/lane AUIs

### Call for action

- We need a clear process of adopting a loss budget

- Proposals in terms of lengths and IL (assuming PAM4); detailed results with Sparameters would help

- Explain the targeted application (switch, NIC, other)

- Until we adopt a loss budget we can't make any decisions on device electrical parameters (including reference Tx/Rx) or even modulation

- Proposals in this area may be premature

- Let's not intermix these steps (e.g. run COM analysis on channels before loss budget is adopted)

# Questions? Comments?

Thank you