# Further Consideration on PHY Control

Tingting Zhang Huawei Technologies

#### Introduction

- The Master/Slave architecture is commonly used in SPE standard, where the Master uses a local clock while the Slave recovers the clock from the received signal sent by the Master.

- There is a concern about the reliability of the timing lock for the Slave in 802.3dg. Brian proposes to use timers with different transmit signaling (SEND\_U/SEND\_F) during training (<u>Curran\_3dg\_01\_01152025</u>).

- This presentation shares a simple scheme by using SENT\_T as most SPE standards do with times introduced during TRAINNING to ensure stable timing lock. A Capability Exchange state (PMA\_state=10) is added between TRAINING and COUNTDOWN to exchange the capability bits and PFC24 after both receivers are fully up to improve training efficiency.

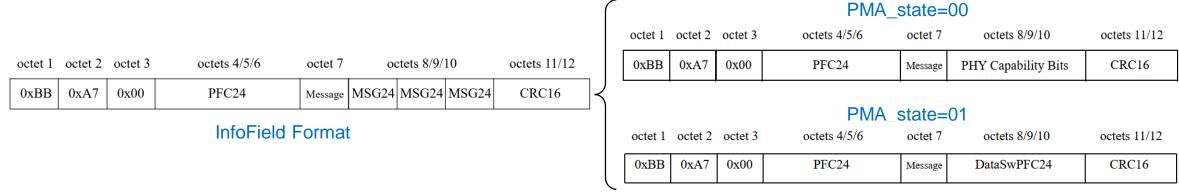

### Traditional InfoField for PHY Control

- For existing SPE standards with PAM2 for training and higher-order PAM (e.g. PAM3/PAM4) for data, the training frame with an embedded InfoField is used for PHY control and frame boundary establishment.

- The InfoField consists of a 3-octet SFD (0xBBA700), 3-octet PFC24, 1-octet Message, 3-octet MAG24 and 2-octet CRC16.

- The 1-octet Message contains the information on the PMA state (PMA\_state), local receiver status, and Slave transmission control or timing-lock result.

- > PMA\_state=00 represents TRAINING. During this stage, the Master and Slave train the receiver and exchange PHY capability. The 3-octet MSG24 in the InfoField carries PHY capability bits.

- > PMA\_state=01 represents COUNTDOWN. DataSwPFC24 in the 3-octet MSG24 is used for format switching.

- PMA\_state=10/11 are reserved.

### **Proposed InfoField Format**

- InfoField is still used for PHY Control during PMA training. PFC24 and COUNTDOWN are also used.

- DataSwPFC24 ensures reliable, fast, and accurate recognition of format switching, due to the repeated transmission of the fixed value and sufficient SNR margin bought by PAM2.

- > PFC24 with an increasing step of 16 also improves the robustness to bit errors.

- Considering the link may not be stable during the first stage of TRAINING, PHY capability bits and PFC24 are transmitted after the receiver is fully up (loc\_rcvr\_status=OK and rem\_rcvr\_status=OK).

- Similar to Clauses 97, 149, and 165, the 2-bit PMA\_state (Oct7<7:6>) in the Message field indicates different states during PMA training.

- > PMA\_state=00: TRAINING. Only SFD, Message, and CRC16 are transmitted.

- > PMA\_state=10: CAPABILITY EXCHANGE. PFC24 and PHY Capability bits are transmitted.

- > PMA\_state=01: COUNTDOWN, switching from PAM2 to PAM3.

| octet 1 | octet 2       | octet 3 | octets 4/5/6 | octet 7 | octets 8/9/10 | octets 11/12 |  |

|---------|---------------|---------|--------------|---------|---------------|--------------|--|

| 0xBB    | xBB 0xA7 0x00 |         | RSV          | Message | RSV           | CRC16        |  |

#### PMA\_state=00 (TRAINING)

#### PMA\_state=10 (CAPABILITY EXCHANGE)

| octet 1 | ctet 1 octet 2 octet 3 |  | octets 4/5/6 | octet 7             | octets 8/9/10 | octets 11/12 |  |

|---------|------------------------|--|--------------|---------------------|---------------|--------------|--|

| 0xBB    | 3 0xA7 0x00 PFC24      |  | Message      | PHY Capability Bits | CRC16         |              |  |

#### PMA\_state=01 (COUTDOWN)

| octet 1 | octet 1 octet 2 octet 3 |  | octets 4/5/6 | octet 7     | octets 8/9/10 | octets 11/12 |  |  |

|---------|-------------------------|--|--------------|-------------|---------------|--------------|--|--|

| 0xBB    | 0xA7 0x00 PFC24         |  | Message      | DataSwPFC24 | CRC16         |              |  |  |

### Updated Message Field

- The 1-octet Message is similar to Clauses 97, 149, and 165, but adds PMA\_state=10 for Master and Slave. The timing\_lock\_OK<4> bit is replaced by a reserved bit 0.

- The Slave starts transmission after min\_slave\_slient\_timer and en\_slave\_tx=1, ensuring sufficient time for Master echo canceller training, and Slave equalizer training and timing locking.

- Master\_init\_timer and Slave\_init\_timer are used during the first stage of training to ensure sufficient time for stable timing lock.

|    | octet 1                             |        | octet 3 | octets 4/5/6       |                   | octet 7 | 0     | octets 8/9/10 |             | octets 11/1          | 2              |

|----|-------------------------------------|--------|---------|--------------------|-------------------|---------|-------|---------------|-------------|----------------------|----------------|

|    | 0xBE                                | 3 0xA7 | 0x00    | RSV/.              | PFC24             | Message | MSG24 | MSG24         | MSG24       | CRC16                |                |

|    |                                     |        | Ма      | ster Messag        | e Field           |         |       | Slave M       | +<br>essage | Field                |                |

| _  | PMA_state loc_rcvr_status <7:6> <5> |        | tatus   | en_slave_tx<br><4> | reserved<br><3:0> |         |       |               |             | c_rcvr_status<br><5> | reserved <4:0> |

| 00 | )                                   | 0      |         | 0                  | 0000              |         |       | 00            |             | 0                    | 00000          |

| 00 | 00 0                                |        |         | 1                  | 0000              | _       |       | 00<br>10      |             | 1                    | 00000          |

| 00 | 00 1                                |        |         | 1                  | 0000              | _       |       |               |             | 1                    | 00000          |

| 10 | )                                   | 1      |         | 1                  | 0000              | _       |       | 01            |             | 1                    | 00000          |

| 01 | 1                                   | 1      |         | 1                  | 0000              |         | L     |               | <b>I</b>    |                      | <u> </u>       |

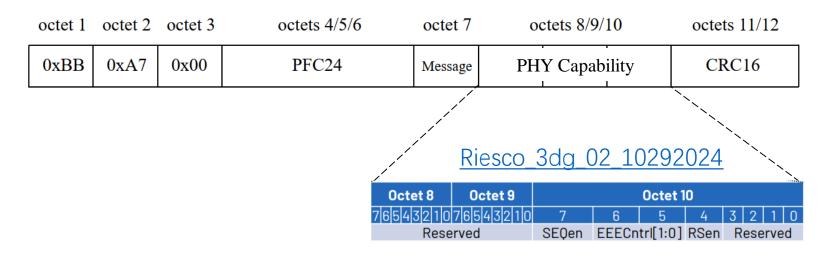

### **PHY Control Infofield**

- During CAPABILITY EXCHANGE (PMA\_state=10), 3-octet PFC24 (octets 4/5/6) and PHY capability bits (octets 8/9/10) are sent.

- > PHY Capability includes the RS-FEC, EEE, LPI, and sequence order set support capability. The SLAVE shall synchronize its partial PHY frame count (PFC24) to the MASTER's PFC24.

- 3-octet DataSwPFC24 during COUNTDOWN (PMA\_state=01) shall be set to an integer multiple of 16.

- SEQen advertises support for sequence ordered sets

- EEECntrl[1:0] advertises the EEE abilities

- RSen advertises support for RS-FEC

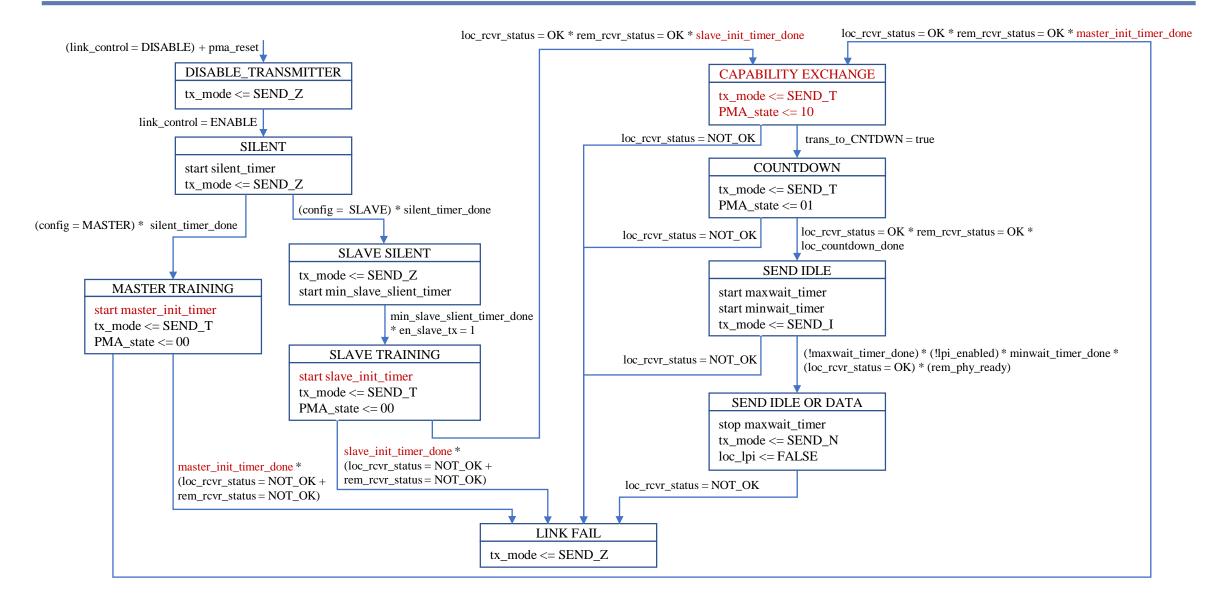

### **Transmit Signaling**

- SEND\_Z: transmission of zero code groups in the DISABLE\_TRANSMITTER state, SILENT state, SLAVE\_SILENT state and LINK\_FAIL state.

- **SEND\_T:** transmission of PAM2 code groups in MASTER/SLAVE TRAINING state, CAPABILITY EXCHANGE state, and COUNTDOWN state. The PAM2 sequence is generated using from 4B6B encoding and the nibble-wise scrambled training frame.

- **SEND\_I:** transmission of PAM3 Idle code groups in SEND IDLE state. The PAM3 symbols are generated using 8B6T with 8N/(8N+1) block corresponding to the idle mode with loc\_phy\_ready = TRUE/FALSE.

- SEND\_N: transmission of PAM3 symbols in SEND IDLE OR DATA state. The PAM3 symbols are generated using 8b6T with 8N/(8N+1) block representing normal MII Data Stream, Control Information, or idle.

#### **State Diagram Parameters**

- silent\_timer: A timer used to determine the amount of time the PHY Control state diagram stays in the SILENT state. The timer shall expire 1 ms  $\pm$  1 µs after being started.

- min\_slave\_slient\_timer: A timer used to determine the minimum amount of time the PHY Control state diagram stays in the SLAVE\_SILENT state. The timer shall expire 10 ms ± 10 µs after being started.

- master\_init\_timer: A timer used to determine the amount of time the PHY Control state diagram stays in the MASTER\_TRAINING state. The timer shall expire 50 ms  $\pm$  10 µs after being started.

- slave\_init\_timer: A timer used to determine the amount of time the PHY Control state diagram stays in the SLAVE\_TRAINING state. The timer shall expire 40 ms ± 10 µs after being started.

- minwait\_timer: A timer used to determine the minimum amount of time the PHY Control state diagram stays in the SEND\_IDLE state. The timer shall expire 5 ms ± 5 μs after being started.

- maxwait\_timer: A timer used to limit the amount of time during which a receiver dwells in the SEND\_IDLE state. The timer shall expire 10 ms ± 5 µs after being started.

- trans\_to\_CNTDWN: This variable indicates whether a valid InfoField containing PHY capability bits has been received.

- **loc\_countdown\_done:** This variable is set to false when the PHY Control state diagram is in the DISABLE\_TRANSMITTER state and is set to true immediately after transmitting the last bit of the DataSwPFC24–1 partial PHY frame.

#### **PHY Control State Diagram**

#### Conclusion

- PHY Control for 100BASE-T1L is similar to Clauses 97, 149, and 165, using InfoField with partial frame counter (PFC24).

- PFC24 and DataSwPFC24 allows reliable, fast, and accurate recognition of format switching and is more robust to bit errors due to the regular value and transmitting PAM2.

- To improve training success probability, timers are introduced to Master and Slave TRAINING state (PMA\_state=00), ensuring sufficient time to achieve stable timing lock.

- The timing\_lock bit in the Slave Message field can be replaced by a reserved bit 0.

- After both receivers are fully up, the capability bits and PFC24 are transmitted to improve training efficiency. The CAPABILITY EXCHANGE state (PMA\_state=10) is added between TRAINING and COUNTDOWN.

- As long as one valid InfoField containing PHY capability bits is received, it moves to COUNTDOWN.

- DataSwPFC24 can be greatly reduced to e.g. 128.

## Q & A