# Clause 184: Test Vectors for 800GBASE-LR1

Elvio Serrano, Victor Trasobares, Kishore Kota – Marvell Semiconductor

P802.3dj Plenary Meeting, Montreal, Canada, July 2024

#### Introduction

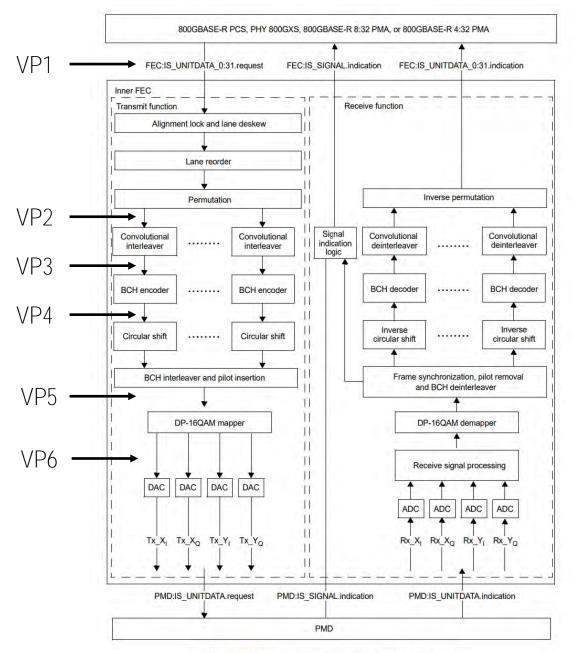

- This contribution provides test vectors for 800GBASE-LR1 Inner FEC transmit function as described in Clause 184. Following functions are included in these vectors:

- Permutation

- Convolutional interleaver

- BCH encoder

- Circular shift

- BCH interleaver

- DSP frame

- Pilot sequence and

- DP-16QAM mapper

- Input stimulus

- 800GBASE-R IDLE signal encoded per Clause 172

#### **Vector Points**

- Vector files are provided for the following points

- VP1: Input to the FEC sublayer

- VP2: Input to the convolutional interleavers

- VP3: Input to the BCH encoders

- VP4: Output of the BCH encoders

- VP5: BCH interleaver and pilot insertion

- VP6: After DP-16QAM mapper

## VP1 Description

- VP1: input-bits (vp1.txt)

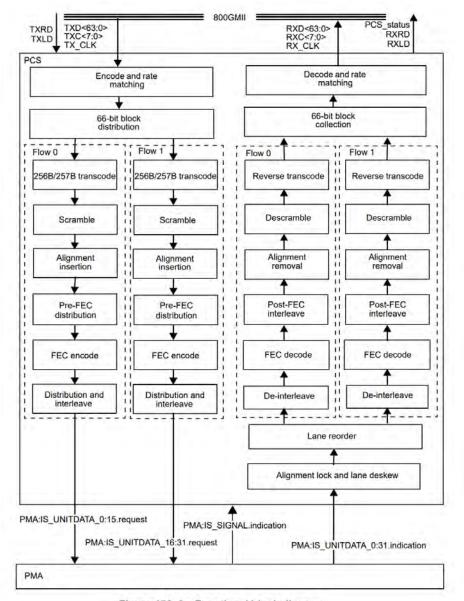

- 800GBASE-R signal is generated by feeding IDLE at the 800GMII interface (at the top of the Fig 172-2)

- The vector file starts with alignment markers (AM)

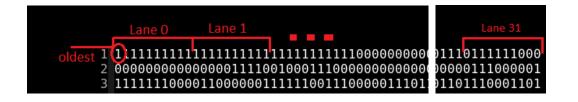

- Each row of the VP1 file has 320 bits, i.e. 32 RS symbols, one per PCS lane. The first 10 bits belong to PCS Lane 0, the second 10 bits belong to PCS Lane 1, and so on. The first bit is the oldest one.

Figure 172–2—Functional block diagram

IEEE P802.3dj Task Force, July 2024

# VP2/VP3 Description

- VP2: after "Permutation" block shown in Fig 184-2 (vp2.txt)

- Same file format as vp1: N rows by 320 columns. The first 10 bits belong to PCS Lane 0, the second 10 bits belongs to PCS Lane 1, and so on. The first bit is the oldest one.

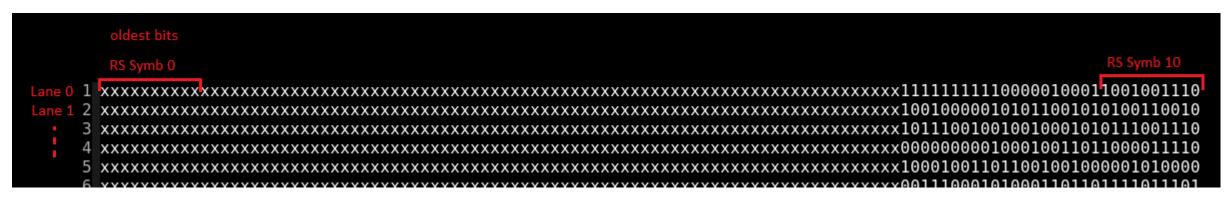

- VP3: after "Convolutional Interleaver" shown in Fig 184-2 (vp3.txt)

- Each row has the 110 bits that feed each of the 32 BCH encoders.

- Xs at the beginning of the file means undetermined value due to Cl's delays

# VP4/VP5 Description

- VP4: after "BCH encoder"s shown in Fig 184-2 (vp4.txt)

- Same file format as vp3, but 16-bit parity is added to the end of each row.

- VP5: after "BCH Interleaver" prior to pilot insersion (vp5\_xi.txt, vp5\_xq.txt, vp5\_yi.txt and vp5\_yq.txt)

- There are four separate files, one per component (xi, xq, yi and yq)

- Each row has 126 bits (i.e., 63 symbols), starting from the oldest one.

### VP6 Description

- VP6: after pilots insertion (vp6\_xi.txt, vp6\_xq.txt, vp6\_yi.txt and vp6\_yq.txt)

- There are also four separate files, one per component (xi, xq, yi and yq)

- Each row has 128 bits (i.e., 64 symbols), the first symbol of each row is the pilot.

- The vectors follow the pilot sequence described Table 184-2.

- VP6 Symbols: after mapping (vp6\_symbols.txt)

- There is one extra file that contains the symbols after mapping.

- The mapping from bit pairs to four-level signal follows Table 184-3

- There are 4 columns per row that contains xi, xq, yi, and yq symbols, respectively.

## Summary

- Test vectors are proposed for inclusion in Annex 184A

- Vectors are provided in companion zip file:

https://grouper.ieee.org/groups/802/3/dj/public/24\_07/kota\_3dj\_04\_2407.zip

Thank you!