# Test Patterns for Inner FEC(s)

### - Clause 177, 184 and Annex 174A

Comment # 9, 10, 128, 148, 149, 150, 345

Xiang He, Huawei

# Background

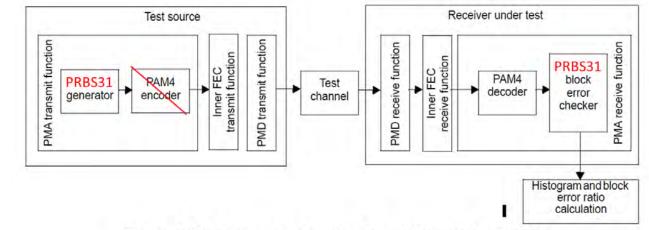

- There are generally two types of test patterns in P802.3dj:

- Those used to verify functionality of the logic, like scrambled zeros, scrambled idles, PRBS31, etc.

- Transmit side (logic) sends known pattern and received side (logic) checks for expected behavior, with the ability to check for bit errors.

- Those used to test a PAM4 PMD, like PRBS31Q, SSPRQ, etc.

- PRBS patterns mapped to PAM4 symbols are applied to PAM4 encoders.

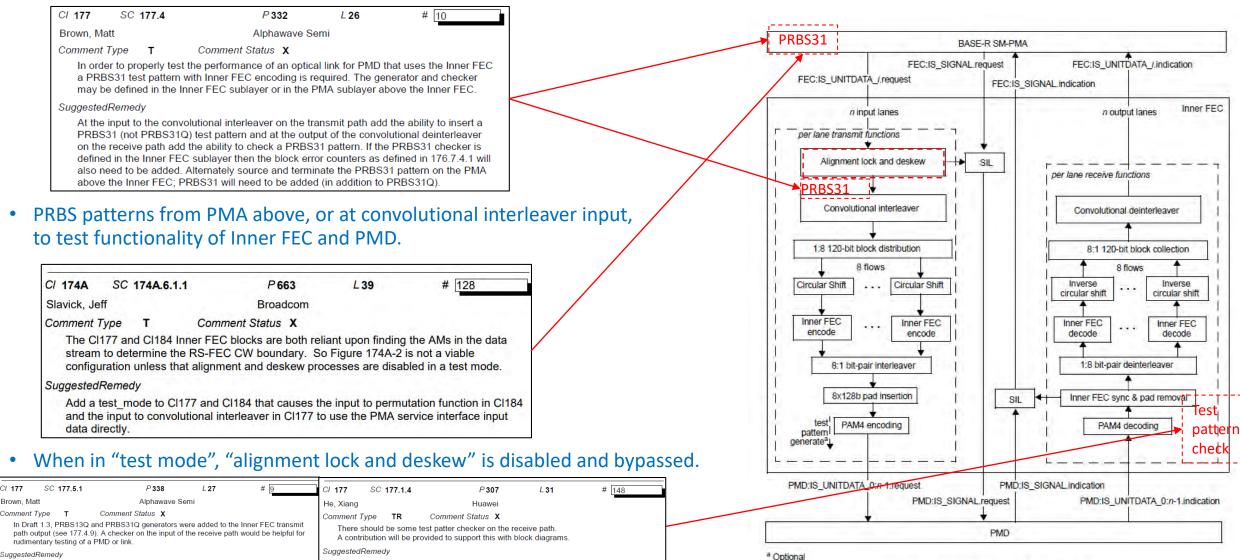

### Test pattern related comments against Clause 177

#### • Add PRBS checker on the Rx

Add PRBS13Q and PRBS31Q pattern checkers to the input of the Inner FEC receive path

Add "test pattern check" on the receive path on the PAM4 decode box, similar as in Figure

176-1

Figure 177-2—Functional block diagram

### Test pattern related comments against Clause 184

| CI 184    | SC 184.2        | P 517                                                             | L 34            | # 149     |

|-----------|-----------------|-------------------------------------------------------------------|-----------------|-----------|

| He, Xiang |                 | Huawei                                                            |                 |           |

| Comment   | Туре Т          | Comment Status X                                                  |                 |           |

| Clause    | e 814 Inner FEC | for 800GBASE-LR1 did not i                                        | nclude any test | patterns. |

| Suggested | IRemedy         |                                                                   |                 |           |

|           | P-16QAM mappe   | at least one test pattern for th<br>r box. Also insert a subclaus |                 |           |

| Pattern | Pattern description                                               | Defined in        |

|---------|-------------------------------------------------------------------|-------------------|

| 5       | Scrambled idle test pattern encoded by the 800GBASE-LR1 Inner FEC | 172.2.4.11, 184.4 |

| 7       | Valid 800GBASE-R signal encoded by the<br>800GBASE-LR1 Inner FEC  | 184.4             |

- Table 185-10 listed test patterns for Clause 184, but no test patterns were in clause 184.

- Recommend to add a PRBS31 test pattern to test the logic functions.

| C/ 174A     | SC      | 174A.6.1.1  | P6                     | 63           | L 39        | # 128                                                            |

|-------------|---------|-------------|------------------------|--------------|-------------|------------------------------------------------------------------|

| Slavick, Je | ff      |             | Broad                  | lcom         |             |                                                                  |

| Comment     | Туре    | т           | Comment Status         | x            |             |                                                                  |

| stream      | to det  | termine the | <b>RS-FEC CW bound</b> | dary. So Fig | jure 174A-2 | y the AMs in the data<br>is not a viable<br>bled in a test mode. |

| Suggested   | Reme    | dy          |                        |              |             |                                                                  |

|             | e input | to convolut |                        |              |             | utation function in CI184<br>ervice interface input              |

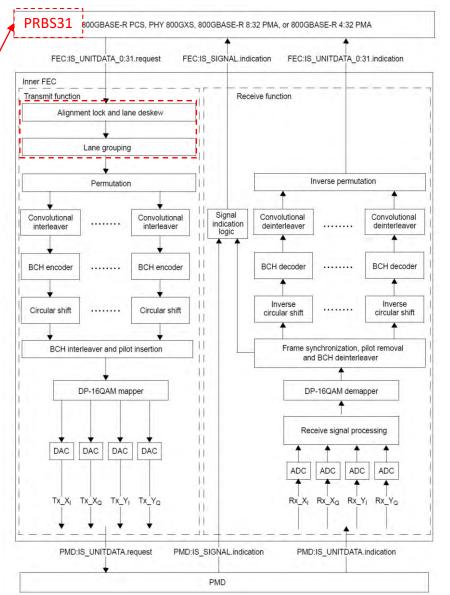

• When in test mode, "alignment lock and lane deskew" and "lane grouping" are disabled and bypassed.

## Test pattern related comments on other clauses

| C/ 182    | SC 182.9.1       | P 481                                                                                         | L 9              | # 345                    |

|-----------|------------------|-----------------------------------------------------------------------------------------------|------------------|--------------------------|

| Ran, Adee | e                | Cisco                                                                                         |                  |                          |

| Comment   | Type TR          | Comment Status X                                                                              |                  |                          |

|           |                  | n 177.4.9.2 is PRBS31Q witho<br>o include the Inner FEC encod                                 |                  | C encoding. In contrast, |

| Table     | 182-17 says RS   | and SRS can be tested with                                                                    | either pattern 3 | or pattern 5.            |

|           |                  | error ratio in either of these te<br>be achieved for per-lane testir                          | · ·              |                          |

| seem      | like a desirable | he pre-FEC BER with PRBS3<br>test, but this cannot be the no<br>errors that the PMD's receive | rmative require  |                          |

| Suggested | dRemedy          |                                                                                               |                  |                          |

| refere    |                  | 3 in 177.4.9.2 to include the is PRBS31Q and specify that to this signal.                     |                  | 0, 0                     |

| C/ 174A   | SC 1                  | 74A.6.1.1                   | P 6                                      | 63  | L 43                             | # 150               |

|-----------|-----------------------|-----------------------------|------------------------------------------|-----|----------------------------------|---------------------|

| He, Xiang |                       |                             | Huaw                                     | /ei |                                  |                     |

| Comment T | уре                   | TR                          | Comment Status                           | Х   |                                  |                     |

| maintai   | in its ch<br>entation | aracteristic<br>will be pro | s.                                       | the | Inner FEC transmit f             | unction in order to |

| 00        | emove "               | PAM4 enc                    | oder" box. Then, e<br>e "Inner FEC trans |     | change "PRBS31Q"<br>unction" box | to "PRBS31", or     |

• Comment #345 is against Clause 182, but suggested remedy is written for clause 177. This can be resolved using response to comment #10.

• Comment #150 is essentially the same thing as comment #10 but focused on the diagram in 174A.

### Suggested changes for Clause 177

- A PRBS31 test pattern may be optionally generated and detected in the PMA above (colocated PMA).

- Dedicated PRBS31 generator per PMAL. No special requirement on seeds.

- "Alignment lock and deskew" is disabled and bypassed when in test mode.

- Proposed text changes: (#10, #128)

Proposed changes to Figure 177-2: (#9, #148)

Insert following subclause before 177.4.9.1:

#### 177.4.9.1 PRBS31 encoded by Inner FEC

The Inner FEC may optionally support a test mode, where a PRBS31 test pattern generated from each PMA lane above (see 176.7.4) is processed by Inner FEC sublayer, with the exception that the alignment lock and deskew function on the transmit path (see 177.4.1) is disabled and bypassed. On the receive path, the PMA above may detect the PRBS31 pattern recovered by the Inner FEC sublayer.

Insert following subclause before 177.5.1:

#### 177.5.1 Test pattern checkers:

The Inner FEC may optionally include test pattern checkers for PRBS13Q and PRBS31Q (see Figure 177-2). Hard-decision PAM4 decoding results are used for test pattern checkers.

### Suggested changes for Clause 184

- A PRBS31 test pattern may be optionally generated and detected in the PMA above (colocated PMA).

- Since there is only one PMD lane, there is no need to provide PMAL based test patterns.

- "Alignment lock and lane deskew" and "lane grouping" are disabled and bypassed when in test mode.

- Proposed text to add a PRBS31 test pattern:

#### 184.4.12 Inner FEC test patterns

#### 184.4.12.1 PRBS31 encoded by Inner FEC

The Inner FEC may optionally support a test mode, where a PRBS31 test pattern generated from the PMA above (see 176.7.4) is round-robin distributed to pcsla[q] for q=0 to 31, and then processed by Inner FEC sublayer, with the exception that the "alignment lock and lane deskew" (see 184.4.1) and "lane grouping" (see 184.4.2) functions on the transmit path are disabled and bypassed. On the receive path, the PMA above may detect the PRBS31 pattern recovered by the Inner FEC sublayer.

### Suggested remedies for comment #128, 150

- Change PRBS31Q to PRBS31.

- Remove the "PAM4 encoder" box in the test source.

- In 177.4.2 add this paragraph after the first paragraph:

When in test mode the convolutional interleaver uses the Inner FEC service interface inputs directly. The selection of the 40-bit symbol boundary point is implementation specific.

• In 184.4.2 add this paragraph at the end:

When in test mode the data received on each of the Inner FEC service interface inputs (FEC:IS\_UNITDATA\_0:31.request) is mapped to pcsla[q] for q=0 to 31.

Figure 174A–2—Test configuration for a PMD with Inner FEC

# Thank you!