## Error ratio for coherent PHY types Draft 1.4 comments 16, 115, 117, 118

Matt Brown, Alphawave Semi

## Supporters

• Adee Ran, Cisco

## Introduction

- Addresses Draft 1.4 comments 115, 117, and 118 related to the 800GBASE-LR1 Inner FEC PRBS31 generator and checker, including adding block error checking to the checker.

- Addresses Draft 1.4 comments 16 related to the allocation of error ratios for an 800GBASE-ER1/ER1-20 Physical Layer implementation.

# Part 1

## PRBS31 test pattern and block error ratio for 800GBASE-LR1 Comments 115, 117, 118

## Comments

| C/ 184                                                                        | SC 184.4.3                                                                                                                            | P 520                                                                                                                                                                     | L 25                                     | # 118                |

|-------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|----------------------|

| Brown, Ma                                                                     | tt                                                                                                                                    | Alphawave Se                                                                                                                                                              | emi                                      |                      |

| Comment                                                                       | Туре Т                                                                                                                                | Comment Status X                                                                                                                                                          |                                          |                      |

| Howev                                                                         |                                                                                                                                       | generator was added in D1.4<br>m can be used for block erro                                                                                                               |                                          |                      |

| Suggested                                                                     | Remedy                                                                                                                                |                                                                                                                                                                           |                                          |                      |

|                                                                               |                                                                                                                                       | C may optionally include a P<br>Ill include a PRBS31"                                                                                                                     | RBS31"                                   |                      |

| Proposed I                                                                    | Response                                                                                                                              | Response Status 0                                                                                                                                                         |                                          |                      |

| C/ 184                                                                        | SC 184.5.10                                                                                                                           | P 530                                                                                                                                                                     | L 49                                     | # 115                |

| 0/ 104                                                                        |                                                                                                                                       |                                                                                                                                                                           |                                          |                      |

| Brown, M                                                                      | att                                                                                                                                   | Alphawave Se                                                                                                                                                              | emi                                      |                      |

|                                                                               |                                                                                                                                       | Alphawave Se<br>Comment Status X                                                                                                                                          | emi                                      |                      |

| Brown, M<br>Commen<br>A PR<br>Howe                                            | t Type <b>T</b><br>BS31 test patterr                                                                                                  | Comment Status X<br>checker was added in D1.4.<br>em can be used for block erro                                                                                           | It is defined as be                      |                      |

| Brown, M<br>Commen<br>A PR<br>Howe<br>PAM                                     | t Type <b>T</b><br>BS31 test patterr<br>ever, this test patt                                                                          | Comment Status X<br>checker was added in D1.4.<br>em can be used for block erro                                                                                           | It is defined as be                      |                      |

| Brown, M<br>Commen<br>A PR<br>Howe<br>PAM<br>Suggeste<br>Char<br>To "T<br>Add | t Type <b>T</b><br>BS31 test patterr<br>ever, this test patt<br>4 PMDs and AUIs<br>adRemedy<br>age "The Inner FE<br>The Inner FEC sha | Comment Status X<br>checker was added in D1.4.<br>em can be used for block erro<br>in 176.7.4.<br>C may optionally include"<br>all include"<br>he PRBS31 checker includes | It is defined as be<br>or ratio measurem | ients as defined for |

. CI 185 SC 185.2 P542 L 39 # 117 Alphawave Semi Brown, Matt Comment Type T Comment Status X Other comments propose that with the addition of the PRBS31 generator and checker in the 800GBASE-LR1 Inner FEC it is now possible to assess the quality detected signal using block error counters similar to the method for PAM4 PMDs and AUIs as defined in 174A.7.1 SuggestedRemedy Update the specification for a PMD receiver in 185.2 accordingly. Provide test configuration and method in 174A. A contribution will be provided. Proposed Response Response Status 0

## 800GBASE-LR1 PHY (single-lane coherent, 10 km)

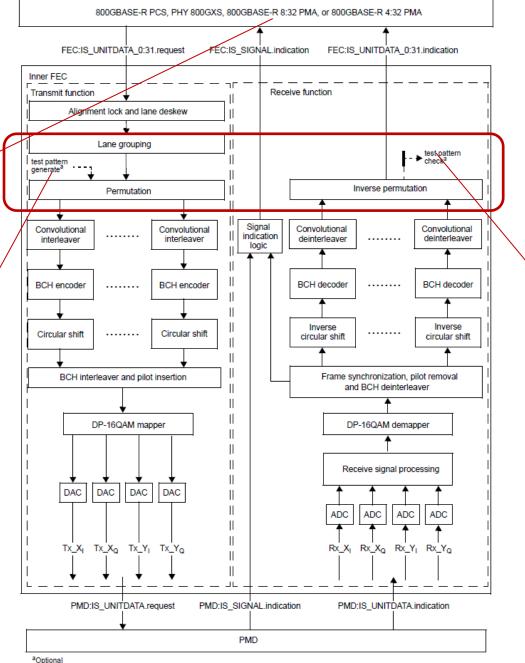

For this Inner FEC, the interface to the sublayer above is 32 PCS lanes, i.e., not one lane per PMD lane

Implement block error counters on the PMA would require 32 instances and they'd all have to be convolved together.

Single PRBS31 pattern generator here

The pattern from a single generator is round-robin distributed to each of the 32 FEC flows.

Single PRBS31 pattern checker here

The pattern from 32 FEC flows is reassembled then processed by the checker.

Corresponds well to the single optical lane.

Change 184.4.3 and 184.5.10 as follows...

#### 184.4.3 Test pattern generator

The Inner FEC-may optionally shall include a PRBS31 test pattern generator (see Figure 184–2). In test mode, 10-bit blocks from the PRBS31 generator are round-robin distributed to the 32 pcsla Inner FEC flows.

The PRBS31 generator implements the free-running PRBS31 pattern defined by Equation 49–2 and shown in Figure 49–9.

If supported the test pattern generator is enabled by the tx\_generator\_enable control variable.

•••

#### 184.5.10 Test pattern checker

The Inner FEC-may optionally shall include a PRBS31 test pattern checker over the inverse permutation output PCS lanes (see 184.4.3). To recover the PRBS31 test pattern, 10-bit blocks are round-robin collected from the 32 inverse permutation function output flows.

If supported the test pattern checker is enabled by the rx\_checker\_enable control variable.

Each PRBS31Q test pattern checker shall include block error detection and 17 related counters. Block error detection and behavior of the counters is defined in 174A.7.

The following counters shall be implemented:

test\_block\_error\_bin\_0\_k

<u>A set of 16 48-bit counters where counter k counts once for each test block received with exactly k errored test symbols, k = 0 to 15. test block error bin 0 16p</u>

A 48-bit counter that counts once for each test block received with 16 or more errored test symbols.

Add the new counters (based on Table 176-9) to Table 184-5 as follows:

| Status variable               | Variable reference | MDIO register/bit number | MDIO register/bit reference |

|-------------------------------|--------------------|--------------------------|-----------------------------|

|                               |                    |                          |                             |

| test_block_error_bin_0_<0:15> | 184.5.10           | 1.2600 to 1.2647         | 45.2.1.213n                 |

| test_block_error_bin_0_16p    | 184.5.10           | 1.2648 to 1.2650         | 45.2.1.213n                 |

|                               |                    |                          |                             |

#### Add new test methods for the 800GBASE-LR1 PMD ISL, based on methods in 174A.7, after 174A.7 as follows...

#### 174A.x Error ratio tests for 800GBASE-LR1 ISLs

This subclause defines test methods for an ISL (see 178B.3) with 800 Gb/s per lane signaling between a pair of 200GBASE-LR1 Inner FEC sublayers including a PMD and Inner FEC at each end and the medium between.

These tests are based on those defined in 174A.7.

#### 174A.x.1 Block error ratio test methods using Inner FEC measurements

#### 174A.x.1.1 Inner FEC block error ratio test configuration

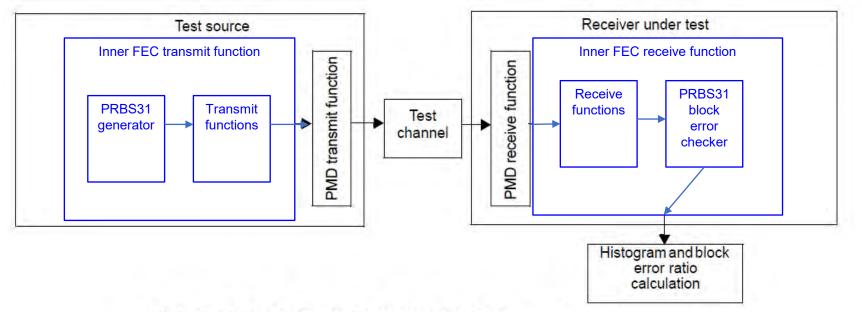

Test configuration for an 800GBASE-LR1 ISL is illustrated in Figure 174A-x.

<Include figure from following slide>

#### 174A.x.1.2 Inner block error counters

The block counters are defined in 174A.7.1.2 with the number of lanes p = 1.

#### 174A.x.1.3 Inner FEC error histogram measurement

Error histograms are measured according 174A.7.1.3.

#### 174A.x.1.4 Inner FEC error mask test method using Inner FEC measurements

Conformance using an error histogram mask is defined in 174A.7.1.5 for a single lane (p = 1).

#### 174A.x.1.5 Block error ratio method for using Inner FEC measurements

Conformance using block error ratio is defined in 174A.7.1.6 for a single lane (p = 1).

The expected block error ratio is met if the measured value is less than the codeword error ratio limit specified in 174A.4 for a PHY-to-PHY link.

#### Update other text in 174A to align, as necessary.

#### IEEE 802.3dj Task Force

Add new test configuration diagram in 174A.x.1.1

Figure 174A-X—Test configuration for 800GBASE-LR1 PMD

Change 185.2 as follows...

#### **185.2 Error ratio allocation**

A complete PHY is expected to meet the frame loss ratio specifications in 174A.5.

A PHY receiver is expected to meet the block error ratio specifications in 174A.8, measured at the PCS, with BER<sub>added</sub> equal to  $3.2 \times 10^{-5}$ .

A PMD receiver is expected to meet the block error ratio specifications in 174A. $\frac{8}{3}$  measured at the <u>PCS Inner FEC</u>, with BER<sub>added</sub> equal to 6.4 × 10<sup>-5</sup>.

# Part 2

### Error ratio allocation for 800GBASE-ER1/ER1-20

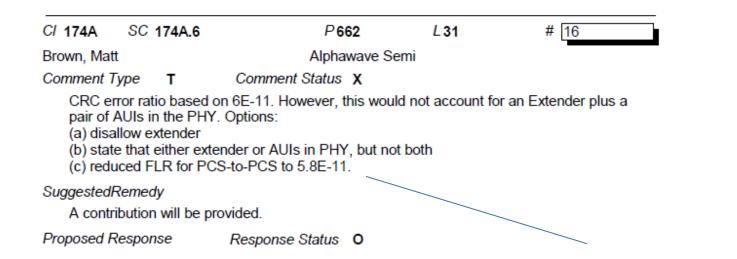

Comments 16

## Comments

Other options:

(d) leave allocations as they are but add a note pointing out that the sum of FLR for the xMII Extender plus the RS-FEC path are unlikely to exceed the allocation for the xMII Extender of 0.1E-11 if compliant AUIs are used.

(e) allocate 0.5E-11 FLR to all xMII Extenders and to RS-FEC path in segmented PHYs like 800GBASE-ER1/ER1-20.

## Comments

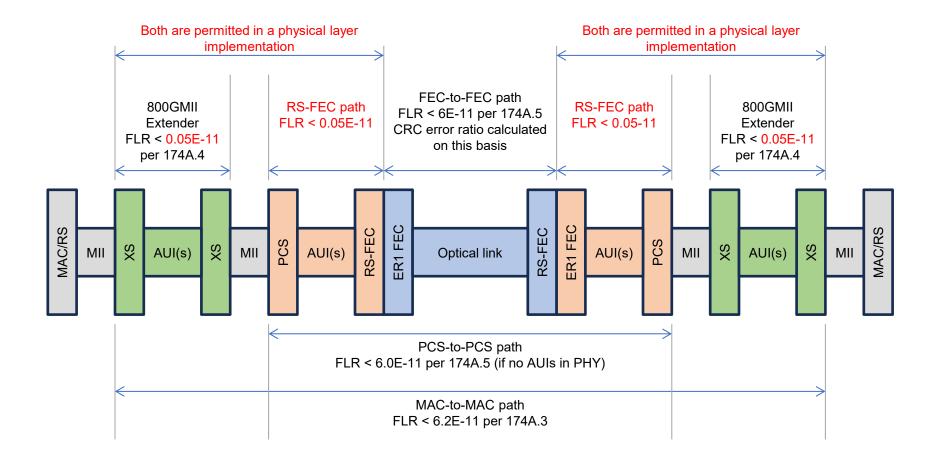

#### Error ratio allocations for 800GBASE-ER1/ER1-20 PHY types...

#### 187.2 Error ratio allocation

A PHY receiver is expected to meet the frame loss ratio specifications in 174A.4.

A PHY receiver is expected to meet the CRC error ratio specified in 174A.6.

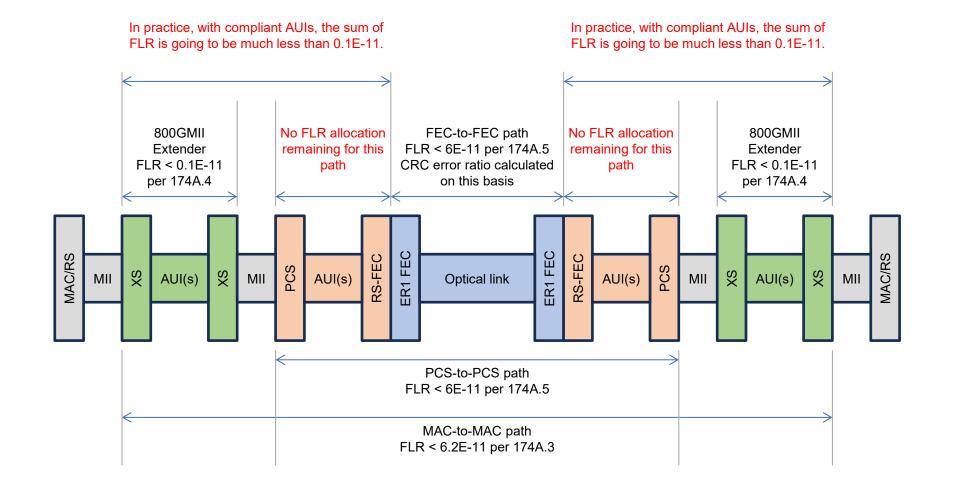

#### 174A.3 Error ratio allocation for an Ethernet network path

Error ratio allocation of the path between two Ethernet DTEs is defined in terms of the frame loss ratio from the PLS service interface of the Reconciliation Sublayer (RS) of the transmitting DTE to the PLS service interface of the RS of the receiving DTE.

The frame loss ratio for 64-octet MAC frames with minimum interpacket gap is expected to be less than  $6.2 \times 10^{-11}$ .

NOTE—The frame loss ratio is affected by multiple components along the network path and is not a normative requirement of a specific component.

#### 174A.4 Error ratio allocation for an xMII Extender

This subclause defines the error ratio allocation for a 200GMII, 400GMII, 800GMII, or 1.6TMII Extender (see Clause 118 and Clause 171).

Error ratio allocation of the xMII Extender is defined in terms of the frame loss ratio between the transmitting XS (DTE or PHY) and the receiving XS (PHY or DTE, respectively).

The frame loss ratio for 64-octet frames with minimum interpacket gap is expected to be less than  $10^{-12}$ . This is equivalent to a FEC codeword error ratio (see 174A.9) lower than  $2.4 \times 10^{-13}$ . If the errors at the input of the RS-FEC are uncorrelated, this is equivalent to a pre-correction BER (*BER*<sub>total</sub>) of  $2.21 \times 10^{-4}$ .

NOTE—The frame loss ratio is affected by multiple components within the xMII Extender and is not a normative requirement of a specific component.

#### 174A.5 Error ratio allocation for a PHY-to-PHY link

Error ratio allocation of a PHY-to-PHY link is defined in terms of the frame loss ratio between the service interfaces of the transmitting PCS and the receiving PCS.

The frame loss ratio for 64-octet MAC frames with minimum interpacket gap is expected to be less than  $6 \times 10^{-11}$ .

For PHYs using the 200GBASE-R, 400GBASE-R, 800GBASE-R, or 1.6TBASE-R PCS, the expected frame loss ratio is equivalent to an FEC codeword error ratio (see 174A.9), as measured at the PCS, of less than  $1.45 \times 10^{-11}$ . If the errors at the input of the RS-FEC are uncorrelated, this is equivalent to a pre-correction BER (*BER*<sub>total</sub>) of  $2.92 \times 10^{-4}$ .

NOTE—The frame loss ratio is affected by multiple components within the PHYs and by the medium, and is not a normative requirement of a specific component.

#### 174A.6 Error ratio allocation for an FEC-to-FEC link

Error ratio allocation of an FEC-to-FEC link, for PHYs that include a segmented FEC sublayer (see 169.2.4c), is defined in terms of the frame loss ratio between the service interfaces of the transmitting FEC and the receiving FEC for FEC sublayers which fully terminate the FEC.

The frame loss ratio for 64-octet MAC frames with minimum interpacket gap is expected to be less than  $6 \times 10^{-11}$ .

For PHYs using the 800GBASE-ER1 FEC, the expected frame loss ratio is equivalent to a CRC error ratio (see 174A.9) of less than  $5.903 \times 10^{-11}$ . If the errors at the input of the FEC are uncorrelated, this is equivalent to a pre-correction BER (*BER*<sub>total</sub>) of  $2 \times 10^{-2}$ .

March 2025

IEEE 802.3dj Task Forc

14

## Current error ratio budgets

Table 174A-1—Error ratio allocations for optical PHYs

| ISL                     | Frame loss ratio<br>for entire<br>PCS-to-PCS link | Codeword error<br>ratio for entire<br>PCS-to-PCS link | BER for entire<br>PCS-to-PCS link<br>(BER <sub>total</sub> ) | BER per ISL <sup>a</sup> |

|-------------------------|---------------------------------------------------|-------------------------------------------------------|--------------------------------------------------------------|--------------------------|

| xAUI-n C2C <sup>b</sup> |                                                   |                                                       |                                                              | 0.08 × 10 <sup>-4</sup>  |

| xAUI-n C2M              |                                                   |                                                       |                                                              | 0.24 × 10 <sup>-4</sup>  |

| PMD-to-PMD              | 6 × 10 <sup>-11</sup>                             | $1.45 \times 10^{-11}$                                | $2.92 \times 10^{-4}$                                        | 2.28 × 10 <sup>-4</sup>  |

| xAUI-n C2M              |                                                   |                                                       |                                                              | $0.24 \times 10^{-4}$    |

| xAUI-n C2C <sup>b</sup> |                                                   |                                                       |                                                              | 0.08 × 10 <sup>-4</sup>  |

<sup>a</sup> Measured at the PMA closest to the PMD or AUI component and after Inner FEC decoding, if present.

<sup>b</sup> If the PMD is a type defined in Clause 180, Clause 181, Clause 182, or Clause 183 (i.e., 200 Gb/s per lane), and xAUI-n C2C is a type defined in Annex 120D (i.e., 50 Gb/s per lane) or Annex 120F (i.e., 100 Gb/s per lane), the xAUI-n C2C is expected to meet the BER allocations in this table.

#### Table 174A-3—Error ratio allocations for xMII Extenders

| ISL        | Frame loss ratio<br>for entire<br>XS-to-XS link | Codeword error<br>ratio for entire<br>XS-to-XS link | BER for entire<br>XS-to-XS link<br>(BER <sub>total</sub> ) | BER per ISL <sup>a</sup> | _ |

|------------|-------------------------------------------------|-----------------------------------------------------|------------------------------------------------------------|--------------------------|---|

| xAUI-n C2C | 0.1 × 10 <sup>-11</sup>                         | $2.4 \times 10^{-13}$                               | $2.21 \times 10^{-4}$                                      | 0.1 × 10 <sup>-4</sup>   |   |

| xAUI-n C2M | 0.1 × 10                                        | 2.4 × 10                                            | 2.21 × 10                                                  | 0.24 × 10 <sup>-4</sup>  |   |

<sup>a</sup> Measured at the PMA closest to the AUI component.

Not accurate. This table is for optical PHYs with concatenated Inner FEC. This table does not apply to optical PHYs with a segmented FEC, like 800GBASE-ER1/ER1-20.

Footnote b is also relevant to the 800GBASE-LR1 PHY. Should fix this.

There is ample margin in the xMII extender budget that might be shared between the xMII extender and the RS-FEC to RS-FEC path on the PHY.

For random BER of 0.34E-4, FLR of 2.5E-25 can be supported on each path. Therefore, in practice, with compliant AUIs, the sum of FLR for the xMII Extender and the RS-FEC path will be far below 0.1E-11.

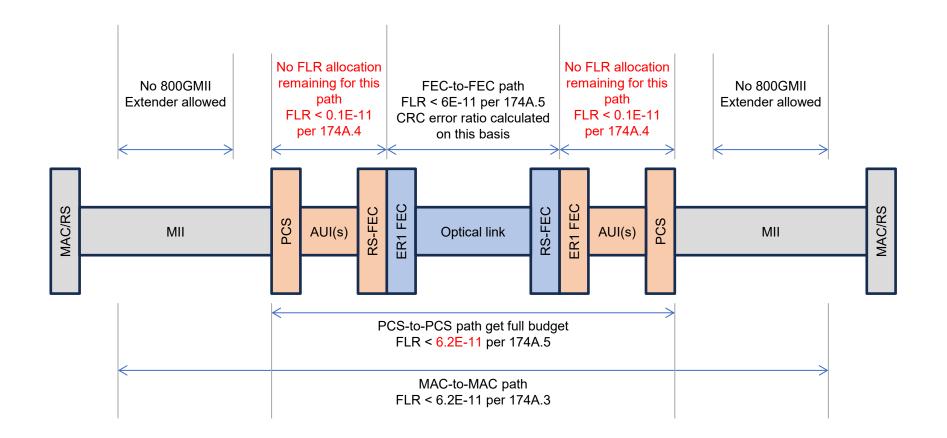

### Draft 1.4 error ratio allocations for 800GBASE-ER1/ER1-20 Physical Layer Implementations

### Option #1: No Extenders allowed.

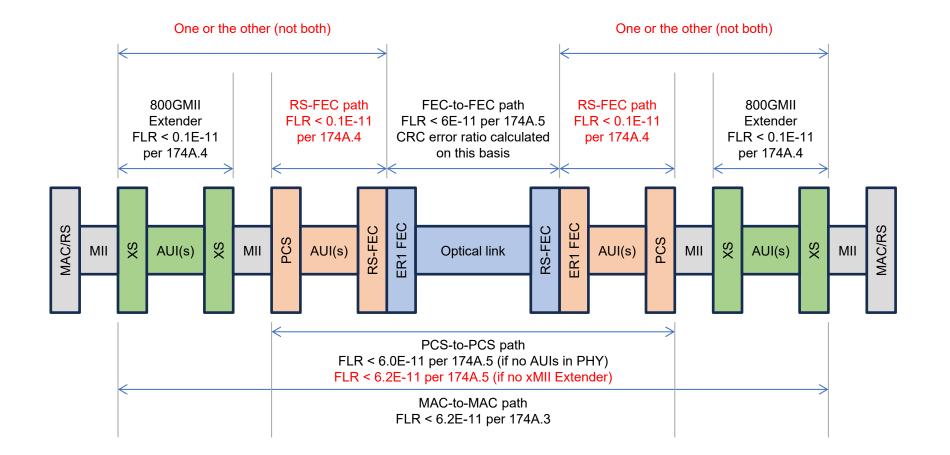

### Option #2: Allow either AUIs in the PHY or Extender, but not both

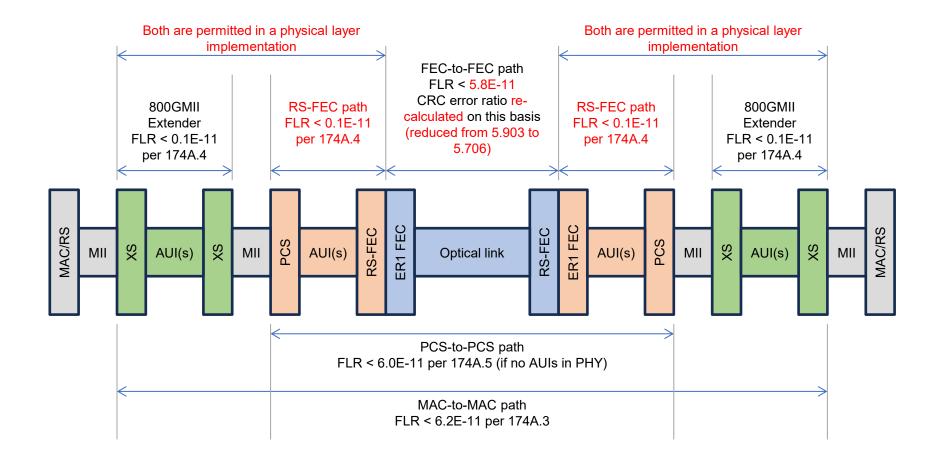

### Option #3: Reduce FLR option for ER1 FEC path

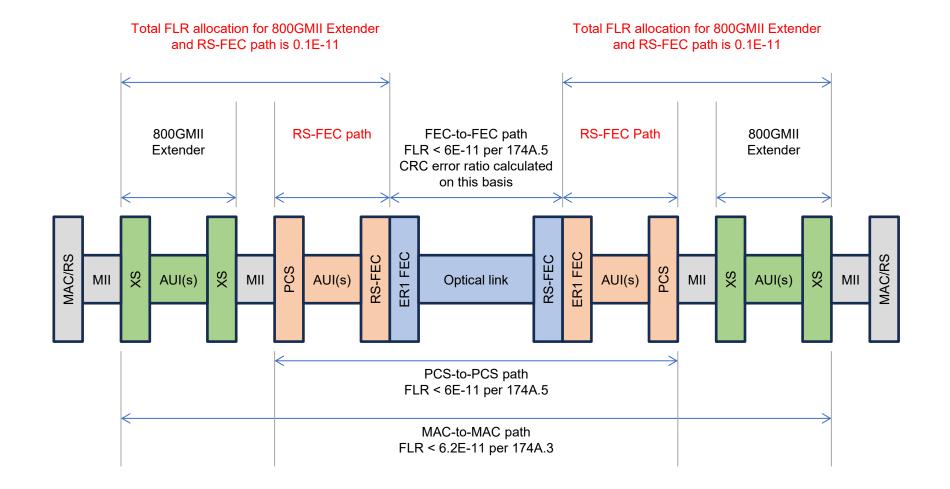

# Option #4: add a note that the FLR allocation for the xMII Extender can be shared with the RS-FEC path

# Option #5: Reduce xMII allocation in half (for all PHY types) and allocate same to RS-FEC path

# Backup slides

Table 187–1—Physical Layer clauses associated with the 800GBASE-ER1-20 and 800GBASE-ER1 PMD

- Exclude 800GMII Extender from Table 187-1. In 174A.4 and Table 174A add that the allocation for

- the xMII Extender also applies to the segment between the 800GBASE-R PCS and the 800GBASE-ER1 FEC.

#### 174A.4 Error ratio allocation for an xMII Extender

This subclause defines the error ratio allocation for a 200GMII, 400GMII, 800GMII, or 1.6TMII Extender (see Clause 118 and Clause 171).

Error ratio allocation of the xMII Extender is defined in terms of the frame loss ratio between the transmitting XS (DTE or PHY) and the receiving XS (PHY or DTE, respectively).

The frame loss ratio for 64-octet frames with minimum interpacket gap is expected to be less than  $10^{-12}$ . This is equivalent to a FEC codeword error ratio (see 174A.9) lower than  $2.4 \times 10^{-13}$ . If the errors at the input of the RS-FEC are uncorrelated, this is equivalent to a pre-correction BER (*BER*<sub>total</sub>) of  $2.21 \times 10^{-4}$ .

NOTE—The frame loss ratio is affected by multiple components within the xMII Extender and is not a normative requirement of a specific component.

| Associated clause        | 800GBASE-ER1-20 and<br>800GBASE-ER1<br>Optional |  |

|--------------------------|-------------------------------------------------|--|

| 90-Time Synchronization  |                                                 |  |

| 170-800 Gb/s RS          | Required                                        |  |

| 170-800GMII <sup>a</sup> | Optional                                        |  |

| 171-800GNII Extendel     | Optional                                        |  |

| 172-800GBASE-R PCS       | Required                                        |  |

| 186-800GBASE-ER1 FEC     | Required                                        |  |

| 186-800GBASE-ER1 PMA     | Required                                        |  |

<sup>a</sup>The 800GMII is an optional interface. However, if the 800GMII is not implemented, a conforming implementation behaves functionally as though the RS and 800GMII were present.

\*The 800GMII Extender, if implemented, extends the 800GMII to the 800GDASE-R PC3 via a physical instantiation.

#### Table 174A-3—Error ratio allocations for xMII Extenders

| ISL        | Frame loss ratio<br>for entire<br>XS-to-XS link | Codeword error<br>ratio for entire<br>XS-to-XS link | BER for entire<br>XS-to-XS link<br>(BER <sub>total</sub> ) | BER per ISL <sup>a</sup> |

|------------|-------------------------------------------------|-----------------------------------------------------|------------------------------------------------------------|--------------------------|

| xAUI-n C2C | $0.1 \times 10^{-11}$                           | $2.4 \times 10^{-13}$                               | $2.21 \times 10^{-4}$                                      | 0.1 × 10 <sup>-4</sup>   |

| xAUI-n C2M | 0.1 ~ 10                                        | 2.4 ^ 10                                            | 2.21 ~ 10                                                  | 0.24 × 10 <sup>-4</sup>  |

<sup>a</sup> Measured at the PMA closest to the AUI component.

٠

Table 187–1—Physical Layer clauses associated with the 800GBASE-ER1-20 and 800GBASE-ER1 PMD

| Add footnote to Table 187-1 that either if there are AUIs |

|-----------------------------------------------------------|

| in the PHY then an 800GMII extender is not permitted —    |

| and vice versa. (Note that D1.4 comment #30 proposes      |

| to add a set of 800GAUI-n to Table 187-1).                |

In 174A.4 and Table 174A add that the allocation for the xMII Extender also applies to the segment between the 800GBASE-R PCS and the 800GBASE-ER1 FEC.

#### 174A.4 Error ratio allocation for an xMII Extender

This subclause defines the error ratio allocation for a 200GMII, 400GMII, 800GMII, or 1.6TMII Extender (see Clause 118 and Clause 171).

Error ratio allocation of the xMII Extender is defined in terms of the frame loss ratio between the transmitting XS (DTE or PHY) and the receiving XS (PHY or DTE, respectively).

The frame loss ratio for 64-octet frames with minimum interpacket gap is expected to be less than  $10^{-12}$ . This is equivalent to a FEC codeword error ratio (see 174A.9) lower than  $2.4 \times 10^{-13}$ . If the errors at the input of the RS-FEC are uncorrelated, this is equivalent to a pre-correction BER (*BER*<sub>total</sub>) of  $2.21 \times 10^{-4}$ .

NOTE—The frame loss ratio is affected by multiple components within the xMII Extender and is not a normative requirement of a specific component.

| Associated clause                 | 800GBASE-ER1-20 and<br>800GBASE-ER1 |

|-----------------------------------|-------------------------------------|

| 90-Time Synchronization           | Optional                            |

| 170-800 Gb/s RS                   | Required                            |

| 170—800GMII <sup>a</sup> C        | Optional                            |

| 171—800GMII Extender <sup>b</sup> | Optional                            |

| 172-800GBASE-R PCS                | Required                            |

| 186-800GBASE-ER1 FEC              | Required                            |

| 186-800GBASE-ER1 PMA              | Required                            |

\*The 800GMII is an optional interface. However, if the 800GMII is not implemented, a conforming implementation behaves functionally as though the RS and 800GMII were present.

<sup>b</sup>The 800GMII Extender, if implemented, extends the 800GMII to the 800GBASE-R PCS via a physical instantiation.

c If one or more 800GAUI-n are implemented in the PHY then an 800GMII Extender is not permitted and vice versa.

#### Table 174A-3—Error ratio allocations for xMII Extenders

| ISL        | Frame loss ratio<br>for entire<br>XS-to-XS link | Codeword error<br>ratio for entire<br>XS-to-XS link | BER for entire<br>XS-to-XS link<br>(BER <sub>total</sub> ) | BER per ISL <sup>a</sup> |

|------------|-------------------------------------------------|-----------------------------------------------------|------------------------------------------------------------|--------------------------|

| xAUI-n C2C | $0.1 \times 10^{-11}$                           | $2.4 \times 10^{-13}$                               | 2.21 × 10 <sup>-4</sup>                                    | 0.1 × 10 <sup>-4</sup>   |

| xAUI-n C2M | 0.1 ~ 10                                        | 2.4 ^ 10                                            | 2.21 ~ 10                                                  | 0.24 × 10 <sup>-4</sup>  |

<sup>a</sup> Measured at the PMA closest to the AUI component.

Change CRC error ratio limit to 5.706E-11. In 174A.4 and Table 174A add that the allocation for the frame loss ratio of 0.1E-11 applies to both the xMII Extender and the segment between the 800GBASE-R PCS and the 800GBASE-ER1 FEC.

#### 174A.4 Error ratio allocation for an xMII Extender

This subclause defines the error ratio allocation for a 200GMII, 400GMII, 800GMII, or 1.6TMII Extender (see Clause 118 and Clause 171).

Error ratio allocation of the xMII Extender is defined in terms of the frame loss ratio between the transmitting XS (DTE or PHY) and the receiving XS (PHY or DTE, respectively).

The frame loss ratio for 64-octet frames with minimum interpacket gap is expected to be less than  $10^{-12}$ . This is equivalent to a FEC codeword error ratio (see 174A.9) lower than  $2.4 \times 10^{-13}$ . If the errors at the input of the RS-FEC are uncorrelated, this is equivalent to a pre-correction BER (*BER*<sub>total</sub>) of  $2.21 \times 10^{-4}$ .

NOTE—The frame loss ratio is affected by multiple components within the xMII Extender and is not a normative requirement of a specific component.

#### 174A.6 Error ratio allocation for an FEC-to-FEC link

Error ratio allocation of an FEC-to-FEC link, for PHYs that include a segmented FEC sublayer (see 169.2.4c), is defined in terms of the frame loss ratio between the service interfaces of the transmitting FEC and the receiving FEC for FEC sublayers which fully terminate the FEC.

The frame loss ratio for 64-octet MAC frames with minimum interpacket gap is expected to be less than  $0 \times 10^{-11}$ .

For PHYs using the 800GBASE-ER1 FEC, the expected frame loss ratio is equivalent to a CRC error ratio (see 174A.9) of less than  $5.903 \times 10^{-11}$ . If the errors at the input of the FEC are uncorrelated, this is equivalent to a pre-correction BER (*BER*<sub>total</sub>) of  $2 \times 10^{-2}$ .

#### Table 174A-3—Error ratio allocations for xMII Extenders

| ISL        | Frame loss ratio<br>for entire<br>XS-to-XS link | Codeword error<br>ratio for entire<br>XS-to-XS link | BER for entire<br>XS-to-XS link<br>(BER <sub>total</sub> ) | BER per ISL <sup>a</sup> |

|------------|-------------------------------------------------|-----------------------------------------------------|------------------------------------------------------------|--------------------------|

| xAUI-n C2C | $0.1 \times 10^{-11}$                           | $2.4 \times 10^{-13}$                               | $2.21 \times 10^{-4}$                                      | 0.1 × 10 <sup>-4</sup>   |

| xAUI-n C2M | 0.1 ~ 10                                        | 2.4 ^ 10                                            | 2.21 ~ 10                                                  | 0.24 × 10 <sup>-4</sup>  |

<sup>a</sup> Measured at the PMA closest to the AUI component.

In 174A.4 and Table 174A add that the allocation for the applies to the combination of xMII Extender and the segment between the 800GBASE-R PCS and the 800GBASE-ER1 FEC.

#### 174A.4 Error ratio allocation for an xMII Extender

This subclause defines the error ratio allocation for a 200GMII, 400GMII, 800GMII, or 1.6TMII Extender (see Clause 118 and Clause 171).

Error ratio allocation of the xMII Extender is defined in terms of the frame loss ratio between the transmitting XS (DTE or PHY) and the receiving XS (PHY or DTE, respectively).

The frame loss ratio for 64-octet frames with minimum interpacket gap is expected to be less than  $10^{-12}$ . This is equivalent to a FEC codeword error ratio (see 174A.9) lower than  $2.4 \times 10^{-13}$ . If the errors at the input of the RS-FEC are uncorrelated, this is equivalent to a pre-correction BER (*BER*<sub>total</sub>) of  $2.21 \times 10^{-4}$ .

NOTE—The frame loss ratio is affected by multiple components within the xMII Extender and is not a normative requirement of a specific component.

Table 174A-3—Error ratio allocations for xMII Extenders

| ISL        | Frame loss ratio<br>for entire<br>XS-to-XS link | Codeword error<br>ratio for entire<br>XS-to-XS link | BER for entire<br>XS-to-XS link<br>(BER <sub>total</sub> ) | BER per ISL <sup>a</sup> |

|------------|-------------------------------------------------|-----------------------------------------------------|------------------------------------------------------------|--------------------------|

| xAUI-n C2C | $0.1 \times 10^{-11}$                           | 2.4 × 10 <sup>-13</sup>                             | 2.21 × 10 <sup>-4</sup>                                    | 0.1 × 10 <sup>-4</sup>   |

| xAUI-n C2M | 0.1 ~ 10                                        | 2.4 ^ 10                                            | 2.21 ~ 10                                                  | 0.24 × 10 <sup>-4</sup>  |

<sup>a</sup> Measured at the PMA closest to the AUI component.

.

- In 174A.4 and Table 174A add that the allocation applies equally to the xMII Extender and the segment between the 800GBASE-R PCS and the 800GBASE-ER1 FEC.

- Change the allocation to FLR 0.05E-11, codeword error ratio 1.2E-13, BER 2.11E-4 and update codeword error ratio and BER columns accordingly.

- No changes are necessary to the AUIs since the BER for the entire XS-to-XS link or RS-FEC-to-ER1 link is sufficient.

#### 174A.4 Error ratio allocation for an xMII Extender

This subclause defines the error ratio allocation for a 200GMII, 400GMII, 800GMII, or 1.6TMII Extender (see Clause 118 and Clause 171).

Error ratio allocation of the xMII Extender is defined in terms of the frame loss ratio between the transmitting XS (DTE or PHY) and the receiving XS (PHY or DTE, respectively).

The frame loss ratio for 64-octet frames with minimum interpacket gap is expected to be less than  $10^{-12}$ . This is equivalent to a FEC codeword error ratio (see 174A.9) lower than  $2.4 \times 10^{-13}$ . If the errors at the input of the RS-FEC are uncorrelated, this is equivalent to a pre-correction BER (*BER*<sub>total</sub>) of  $2.21 \times 10^{-4}$ .

NOTE—The frame loss ratio is affected by multiple components within the xMII Extender and is not a normative requirement of a specific component.

Table 174A-3—Error ratio allocations for xMII Extenders

| ISL        | Frame loss ratio<br>for entire<br>XS-to-XS link | Codeword error<br>ratio for entire<br>XS-to-XS link | BER for entire<br>XS-to-XS link<br>(BER <sub>total</sub> ) | BER per ISL <sup>a</sup> |

|------------|-------------------------------------------------|-----------------------------------------------------|------------------------------------------------------------|--------------------------|

| xAUI-n C2C | 0.1 × 10 <sup>-11</sup>                         | 2.4 × 10 <sup>-13</sup>                             | 2.21 × 10 <sup>-4</sup>                                    | 0.1 × 10 <sup>-4</sup>   |

| xAUI-n C2M | 0.05E-11                                        | 1.2E-13                                             | 2.11E-4                                                    | 0.24 × 10 <sup>-4</sup>  |

<sup>a</sup> Measured at the PMA closest to the AUI component.

# Thanks