### Rethinking the 800GBASE-ER1 model

Tom Huber (Nokia), Gary Nicholl (Cisco), Jeff Slavick (Broadcom), Eugene Opsasnick (Broadcom), Andras deKoos (Microchip), Mike Sluyski (Cisco), Dave Ofelt (Juniper)

1

#### Supporters

- John D'Ambrosia Futurewei, US subsidiary of Huawei

- Matt Brown Alphawave

### How did we get here?

- As we continued to fill in the details for 800GBASE-ER1 and 800GBASE-ER1-20, using a separate ER1 PCS, the following challenges were discovered:

- 800GBASE-ER1 is a new PHY family

- The feature for conveying alignment marker location requires introducing new modes of operation to the 800G XS

- The description of the functions in the XS and ER1 PCS is not well-aligned with anticipated implementations because the interface between the XS and the PCS is the MII, whereas practical implementations are mapping 257b blocks directly into the ER1 frame structure

- The use of the XS cannot be mandated, which increases complexity in the PCS

- These challenges introduce potential schedule risk for WG ballot in May 2025

- There is an alternative architecture that avoids the complexity and mitigates the schedule risk

### Alternative architecture for 800GBASE-ER1

- The challenges are all related to treating ER1 as a separate PCS

- The original rationale for this was based on ER1 having a separate FEC from 800GBASE-R

- Implementations using pluggable modules would utilize a segmented FEC architecture since the AUI will use RS(544,514) FEC and the ER1 link will use something else

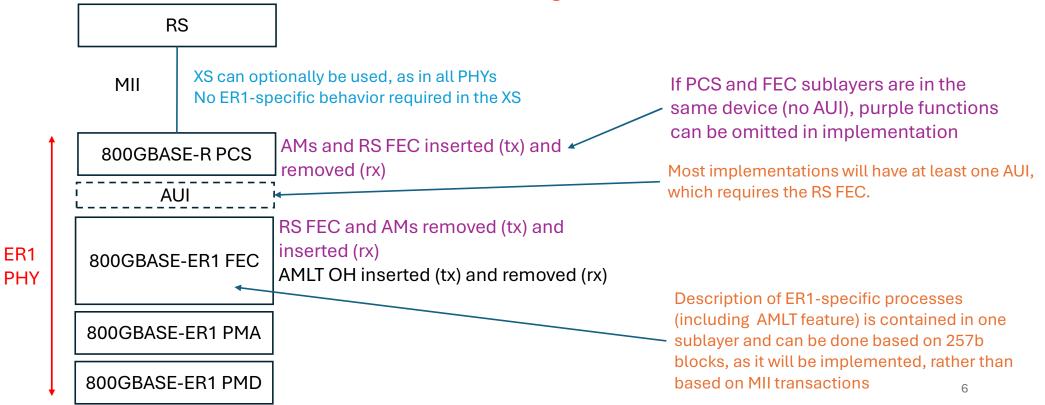

- An alternative is to use the 800GBASE-R PCS and define an 800GBASE-ER1 FEC sublayer that:

- Terminates the RS FEC

- Maps 257b blocks into the ER1 frame and adds the ER1 FEC

- This alternative has the same architecture as 800GBASE-LR1

### Current 800GBASE-ER1 model is not self-consistent across possible PHY configurations

|                                                         | RS               |                                                                                                                                                                                             |                                                                                                      | R                                                               | S                                                                                                                                   |                                                         |

|---------------------------------------------------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|

|                                                         | DTE_XS           |                                                                                                                                                                                             | AMs inserted (tx) and removed (rx)                                                                   |                                                                 | There is no need for the AML feature in this<br>PHY since the problem it solves doesn't exist                                       |                                                         |

|                                                         | PHY_XS           |                                                                                                                                                                                             | AMs removed (tx) and inserted (rx)                                                                   |                                                                 | in this configuration – but we have to consider interworking with the other configuration too.                                      |                                                         |

| RAML signals if AML is used MII to make A               |                  |                                                                                                                                                                                             | information between XS and PCS across the<br>ML feature work, which requires XS to have<br>behavior. |                                                                 | The RS can't provide the special signals the PHY_XS provides for the AML feature since there are no AMs in the RS to remove, so the |                                                         |

| MII rate will be different if Idles are not re-inserted |                  | PHY_XS inserts Idles to compensate for removed AMs, but<br>doing that significantly complicates the AML feature, so it is<br>better to not insert Idles. But we specified the PCS to remove |                                                                                                      | PCS would have to 'fake' the signals if the feature is enabled. |                                                                                                                                     |                                                         |

|                                                         |                  |                                                                                                                                                                                             | we have to insert them or make the PCS behavior<br>nt on whether it connects to an RS or PHY_XS      |                                                                 |                                                                                                                                     |                                                         |

|                                                         | 800GBASE-ER1 PCS |                                                                                                                                                                                             | AMLT OH inserted (tx) and removed (rx)                                                               | 800GBASE-ER1 PCS                                                |                                                                                                                                     | PCS has to remove Idles to create the correct bit rate  |

|                                                         | 800GBASE-ER1 PMA |                                                                                                                                                                                             |                                                                                                      | 800GBASE-ER1 PMA                                                |                                                                                                                                     | PCS either has to be required to disable AML or         |

|                                                         | 800GBASE-ER1 PMD |                                                                                                                                                                                             |                                                                                                      | 800GBASE-ER1 PMD                                                |                                                                                                                                     | has to "fake" the TAML<br>signal if AML is enabled<br>5 |

## Alternative model for 800GBASE-ER1 based on FEC sublayer

This architecture aligns with 800GBASE-FR4, -LR4, and -LR1

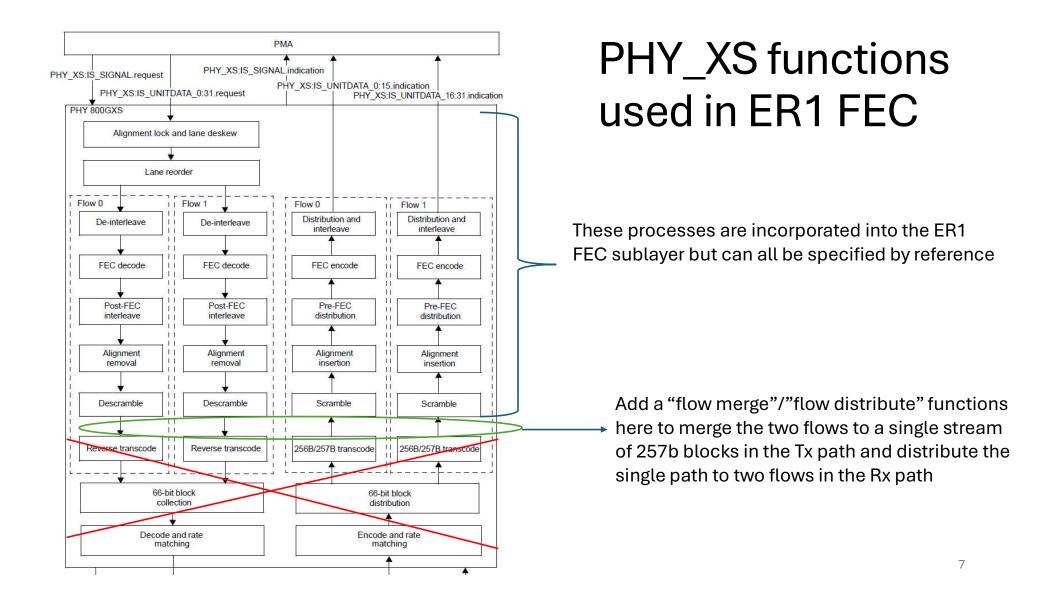

## ER1 PCS functions used in ER1 FEC

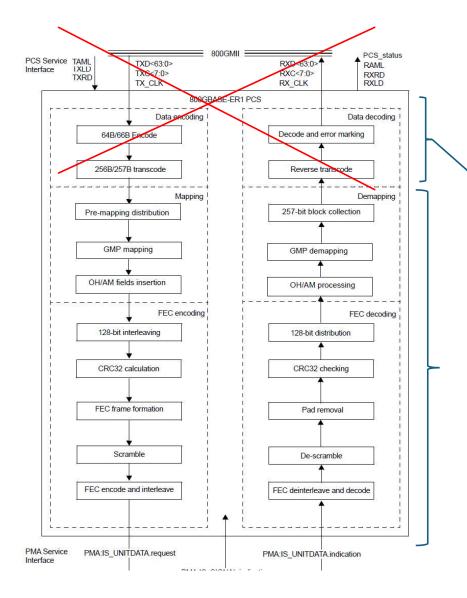

Replace this Data encoding/decoding block with a "Inverse RS FEC" block that uses functions from

the PHY\_XS (see previous slide) plus a "flow merge" function to combine the two flows into a single 257b block stream

No changes needed as a result of changing the architecture to a FEC sublayer, other than in description of AML field in the OH/AM fields insertion function

# Clause 169 changes to reflect alternative architecture

- Update Table 169-1 to indicate that the 800GBASE-ER1 and ER1-20 PHYs use 800GBASE-R encoding

- Update Table 169-3 to change the title of clause 186, and to include clauses 172, 173, 120F, 120G, 176, 176C, 176D as for LR1

- Remove all changes to 169.2.3

- Add a new 169.2.4c to discuss the ER1 FEC

- <text proposal to be added>

- Remove the sentence inserted in 169.3 about PHYs that are not part of the 800GBASE-R family

- In the change to 169.3.2, add "or 800GBASE-ER1 FEC" after "Inner FEC"

- <specific text to be added>

- Add a row to Table 169-4 for ER1 FEC (also a row for the PMA, which is currently missing)

# Clause 171 doesn't need ER1 exceptions

- Remove everything related to the ER1 PCS alignment marker location transparency feature in these locations:

- 171.1.1

- 171.3

- Figure 171-2

- 171.3.3

- 171.6a

- Table 171-2

- Table 171-3

- 171.9.4.6a

### Clause 186: Rename the PCS subclause to an Work in progress... ER1 FEC sublayer clause

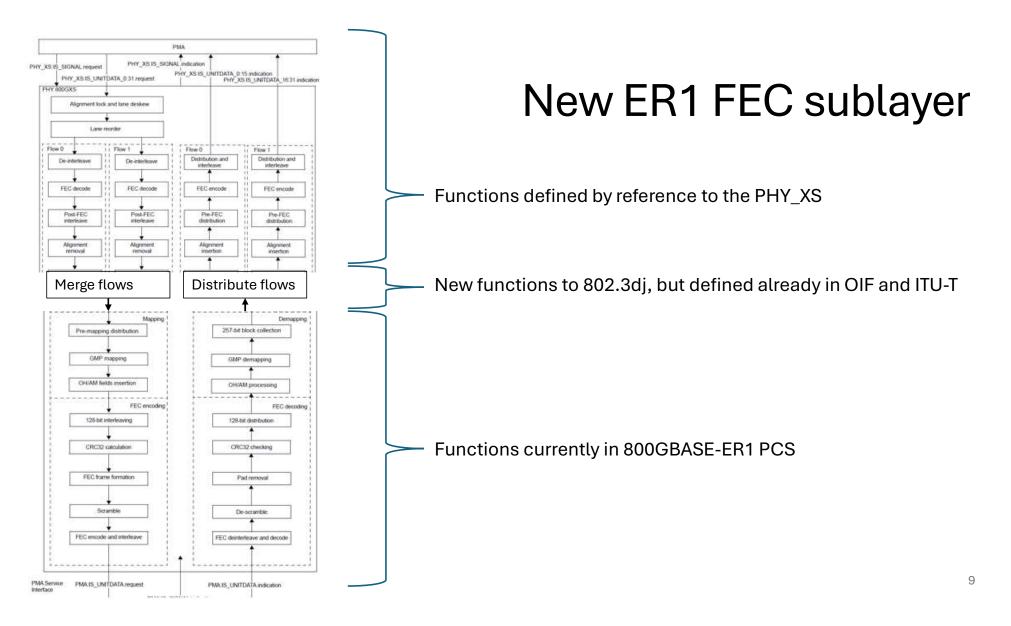

- ER1 FEC sublayer include part of what the PHY\_XS includes

- The ER1 FEC sublayer would be most of what is in the ER1 PCS clause currently:

- Remove 66b encoding/rate adaptation and 257b transcoding

- Rework the AMLT text to be based on 257b blocks rather than MII transactions (the text gets) simpler); all the behavior related to this feature is contained within the ER1 FEC sublayer rather than being split between the XS and the PCS

- Add a function to merge the two flows from the PCS into a single flow prior to mapping with GMP and the corresponding function to distribute to two flows at the demapper (similar to what OIF and ITU already specify)

- The ER1 FEC sublayer is at the same location in the PHY stack as the 'inner FEC' for LR1

- The ER1 FEC sublayer can be specified such that no changes are needed to ER1 PMA

- ER1 FEC and PMA sublayers could be combined as they are in 177 and 184

- Need to consider how frame loss ratio and bit error rate is defined

- If the PCS and FEC are co-located in an implementation, there are further simplifications that can be achieved wrt not literally adding and removing the RS FEC

### AML feature details

- The AML feature is part of the "OH/AM fields insertion" and "OH/AM processing" functions

- We still need to do many of the things in <u>https://www.ieee802.org/3/dj/public/adhoc/optics/1224\_OPTX/sla</u> <u>vick\_3dj\_optx\_01\_241219.pdf</u> to complete specification of the AML feature

- The exact details of what changes need to be made depend on how the ER1 PHY is modeled (and are not the subject of this presentation)

Work in progress...

#### Proposal

- Change the model of ER1 from a PCS to a FEC sublayer

- All 800G PHYs use the same PCS

- All 800G PHYs use the same optional XS

- FEC-specific aspects are captured in FEC sublayers for all PHYs that use FEC beyond/other than RS(544,514)

- Better alignment with real-world implementation enables simpler description

- This is purely a change in documentation structure, not a change in functionality