# TDD Baseline Proposal for 802.3dm (updated)

January 21<sup>st</sup>, 2025 Phoenix, AZ

Ahmad Chini, Broadcom Corporation

Claude Gauthier, NXP

Frank Wang, Realtek

Kamal Dalmia, Aviva Links

Ramanjit Ahuja, Onsemi

Steve Gorshe, Microchip

#### Comments

- Multiple TDD based options for asymmetric Ethernet link was previously presented to the 802.3dm task force<sup>1,2</sup>.

- Many participants and attendees have since shown interest to use the 64/65 encoding and stay with 3GHz/6GHz baud rates and lower complexity FEC.

- This joint presentation consolidates the proposal into a single TDD based solution with a note that the authors are open to further constructive comments from the task force members.

- The parameters are also optimized for ease of implementations.

<sup>1-</sup> https://www.ieee802.org/3/dm/public/1124/Chini 3dm 01a 1124.pdf

<sup>2-</sup> https://www.ieee802.org/3/dm/public/1124/Dalmia Goel 3dm 01a 11112024.pdf

#### **TDD Baseline**

| <b>Ethernet Packets Boundary</b> | 64b/65b encoding                                                                           |

|----------------------------------|--------------------------------------------------------------------------------------------|

| Speed Grades (@ xMII)            | Forward Link: 2.5Gbps, 5Gbps & 10Gbps Reverse Link: 100Mbps (PAM2, 2.5Gbps line rate )     |

| Modulation                       | PAM2 for 2.5Gbps and 5Gbps PAM4 for 10Gbps                                                 |

| Baud Rate                        | 3.0Gsps for 2.5Gbps (forward and reverse link) 6.0Gsps for 5Gbps and 10Gbps (forward link) |

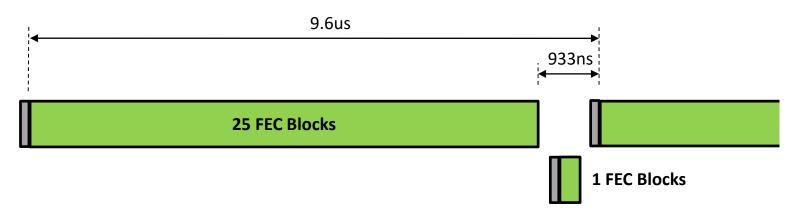

| TDD Cycle                        | 9.6µs for ALL speed grades                                                                 |

| FEC Block Period                 | 346.66ns for ALL speed grades                                                              |

### **TDD Baseline (cntd.)**

| FEC Type                                       | S=8bit Reed-Solomon Code  RS(130S, 122S), L=1 for 2.5Gbps (120Byte at XGMII, 15 x 65b+1b OAM)  RS(130S, 122S), L=2 for 5.0Gbps (240Byte at XGMII, 30 x 65b+2b OAM)  RS(130S, 122S), L=4 for 10Gbps (480Byte at XGMII, 60 x 65b+4b OAM)  L= 2 and 4 shows number of interleaved RS codes |

|------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IBG (Inter Burst Gap) normal mode transmit gap | 2 x 106.66ns                                                                                                                                                                                                                                                                            |

| Total Refresh (Resync) Sequence                | 1120b PAM2 at 3Gsps<br>2240b PAM2 at 6Gsps                                                                                                                                                                                                                                              |

| FIFO                                           | Forward link: 292-Byte at 2.5Gbps 584-Byte at 5.0Gbps 1168-Byte at 10Gbps Reverse link: 116-Byte at 100Mbps                                                                                                                                                                             |

Let's define

Then note that:

T= One TDD Cycle / 360

One FEC Block Period = 13T

IBG = 4T

Total Refresh Period = 14T

## Thank you for your attention!

Questions?