# Exploring Receiver Tradeoffs: 100Mbps and 3Gbps Implementations

Contribution to 802.3dm Task Force

January 22, 2024

TJ Houck (Marvell)

# <u>Topics</u>

- Why does TDD require 3Gbps to transfer only 100Mbps of data?

- Asymmetric Channel Efficiency from TDD

- Receiver Complexity 3Gbps TDD vs 100Mbps ACT

## Why does TDD require 3Gbps to transfer only 100Mbps of data?

#### TDD - Time Division Duplex

Line rate 12Gbps – 10Gbps Data Rate Line rate 6Gbps – 5Gbps Data Rate Line rate 3Gbps – 2.5Gbps Data Rate

Line rate 3Gbps - 100Mbps Data Rate

#### <u>ACT – (Asymmetric Concurrent Transmission) – GMSL and FPD-Link (FDD)</u>

Line rate 11.25Gbps – 10Gbps Data Rate Line rate 5.6Gbps – 5Gbps Data Rate Line rate 2.8Gbps – 2.5Gbps Data Rate

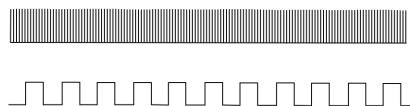

Line rate 117.1875Mbps – 100Mbps Data Rate

Manchester encoded to 234Mbps

### Asymmetric Channel Efficiency of TDD

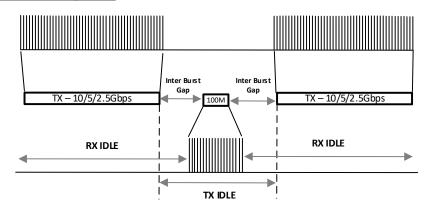

- Inter Burst Gap (IBG)

- Additional delay to avoid interference

- Resync Headers

- Happens every TX and RX cycle

- Overhead

- Larger overhead due to Resync and IBG

- Actual Data throughput 3.3%

- Inefficient use of the Receiver

- Requires Buffer from lack of throughput

- Can not support 1500byte packet transfer

#### TDD - Time Division Duplex - 3Gbps Receive

|                 | 3.0Gbps - TDD           | 100Mbps - (ACT)    | GMSL2 - 187Mbps - (FDD) |

|-----------------|-------------------------|--------------------|-------------------------|

|                 | Repeated                |                    |                         |

|                 | synchronization headers | Once               | Once                    |

| Synchronization | in each RX phase        | During 1st boot    | During 1st boot         |

|                 | Overheaded happens      |                    |                         |

| Resync Header   | every frame TX/RX       | None               | None                    |

| Idle Burst Gap  | 104nsec                 | None - not needed  | None - not needed       |

|                 | >90% - Full Link time   |                    |                         |

| Overhead Impact | 36% - 100Mbps           | ~17%               | ~17%                    |

| Data Bandwidth  | 100Mbps                 | 100Mbps            | ~155Mbps                |

| Throughput      | 3.3% for 3Gbps          | 85.47% for 117Mbps | 83% for 187Mbps         |

|                 | 116bytes                |                    |                         |

|                 | Requires buffer to meet |                    |                         |

|                 | 802.3 compliance        | 64 - 1500 bytes    |                         |

| Packet sizes    | 1500byte packet         |                    | Not Ethernet            |

# Receiver Complexity 3Gbps TDD vs 100Mbps ACT

|                            | 3.0Gbps - TDD            | 100Mbps - (ACT)      | GMSL2 - 187Mbps - (FDD)   |

|----------------------------|--------------------------|----------------------|---------------------------|

|                            | CTLE, LNA, PGA for       | LNA and LPF for      | LNA and LPF for 187Mbps   |

| AFE (Analog Front-End)     | 3Gbps                    | 234Mbps bandwidth    | bandwidth                 |

| CDR (Clock Data Recovery)  | х3                       | x1                   | Baseline                  |

| Equalization               | 1-3 tap DFE              | None                 | None                      |

| Deserializers              | High Speed required      | Basic                | Basic                     |

| Estimated power Disspation | Higher than x4           | x1                   | Baseline                  |

| Die Size                   | Higher than x4.5         | x1                   |                           |

| Process nodes              | Lower Geometry           | Any node             | older node                |

|                            | Difficult - Will require |                      |                           |

| Imager Integration         | Lower Node               | Easier to match node | possible - more difficult |

Numbers for 3Gbps - TDD are conversative – Automotive robustness will most likely increase complexity of circuitry and size

$Referenced: $\frac{https://ieee802.org/3/dm/public/0924/jonsson\ razavi\ 3dm\ 01\ 09\ 15\ 24.pdf}{Referenced: $\frac{https://ieee802.org/3/dm/public/0924/jonsson\ 3dm\ 01\ 09\ 15\ 24.pdf}{Referenced: $\frac{https://ieee802.org/3/dm/public/0924/jonsso$

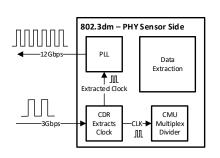

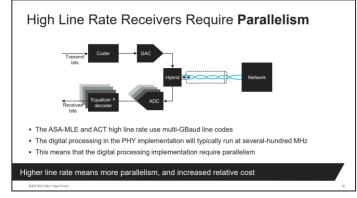

#### TDD - High Level Block Diagram

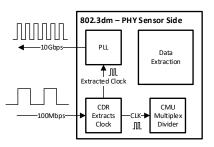

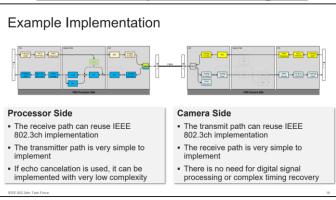

#### **ACT – Example Block Diagram**

## Summary

1

It is proposed to **minimize the 100Mbps receiver** to be competitive in the existing market space

2

It is proposed to **have efficient bandwidth** from Low speed and Highspeed receiver

## Contributors

- Paul Fuller

- David Shen

- Ragnar Jonsson

Essential technology, done right™