# **Considerations for Crystal-less PHY**

IEEE 802.3dm

July, 2025

Hiok Tiaq Ng, Kamal Dalmia Aviva Links Inc.

Page 1

# Contributor

• Ramanjit Ahuja - onSemi

## Introduction

- Crystal-less operation of 802.3dm PHY is desirable to achieve lower relative costs in sensor applications\*

- This contribution looks at several factors impacting ability of PHY RX to operate in a crystal-less manner

- Simple no transistor model used for an ACT analog implementation in SPICE

- BCI noise was injected\*\*

- References

- \* https://www.ieee802.org/3/dm/public/0525/Ng\_3dm\_01\_05122025.pdf

- \*\* https://www.ieee802.org/3/dm/public/1124/Pischl\_3dm\_01a\_1124.pdf

## PHY RX considerations

- Clock must be extracted from incoming low frequency data

- Eye diagram should be maximally open for ease of clock extraction

- Some factors impacting eye closure

- Return Loss, Insertion Loss of MDI and Cable

- BCI noise

- Jitter in Clock/Data signals of SER and DES (not addressed here)

- Residual supply noise through PoC inductors (not addressed here)

- Implementation losses (not addressed here)

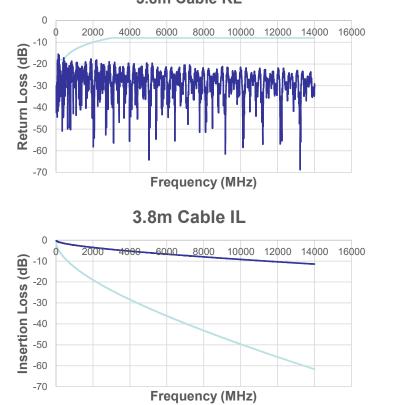

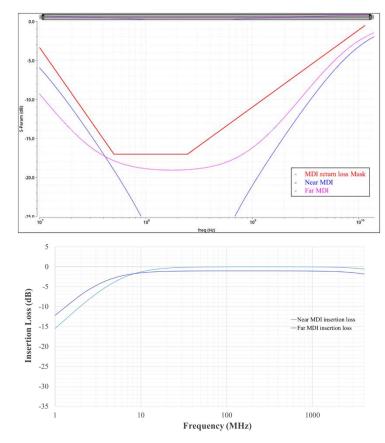

## MDI and Cable models

• Cable RL and IL

#### 3.8m Cable RL

• MDI RL and IL

IEEE 802.3dm –July, 2025

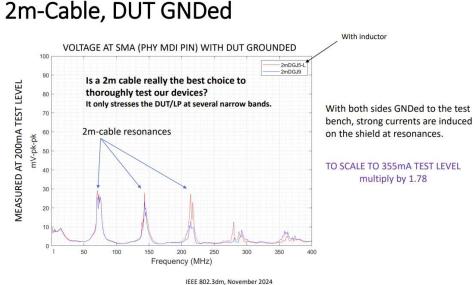

#### **BCI Noise Levels**

- Injected BCI 2m noise levels from <a href="Pischl\_3dm\_01a\_1124">Pischl\_3dm\_01a\_1124</a> excerpted below

- Lowest grounded DUT noise level in presentation

- Did not scale up to 355mA test level

- Used the lower non-inductor peak-to-peak noise level

- Used the lowest 3 noise frequencies

IEEE 802.3dm –July, 2025

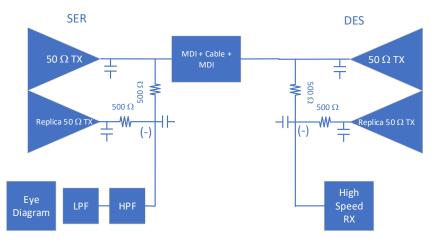

#### Link Model

- PAM4 5.625GSps ↓, 234Mbps ↑

- 0.65Vppse, 0.32Vppse TX output swings

- 50  $\Omega$  TX/RX, 500  $\Omega$  resistive Hybrid

- MDI limits already assume losses from coupling cap and PoC

- 30MHz HPF and 2 Pole 234MHz LPF post Hybrid

- Implemented in differential fashion, but using single ended Coax

| Cable Segment Characteristics | Char Impedance (Ohms) |

|-------------------------------|-----------------------|

| RG174 – 0.35m                 | 48                    |

| RTK031 – 0.4m                 | 52                    |

| RTK031 – 2.4m                 | 48                    |

| RTK031 – 0.35m                | 52                    |

| RG174 – 0.35m                 | 48                    |

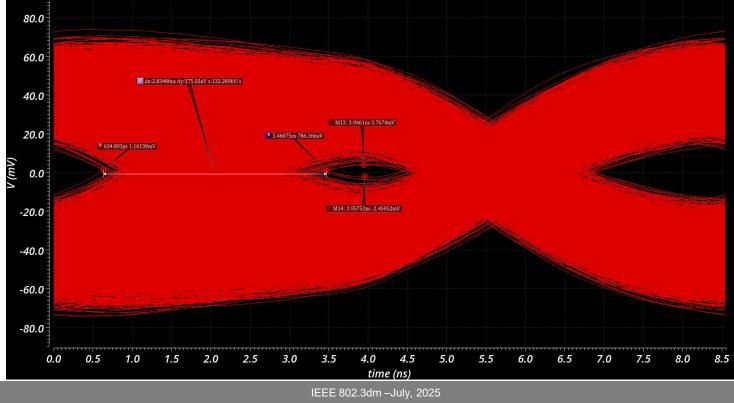

#### **Observed Eye**

- ~100us of ACT upstream data

- One eye is basically closed

- Jitter as simulated ~ 2.8ns

#### Summary

- Simple analog model of ACT RX shows eye closure

- Other impairments not added

- Lower level of BCI noise used

- Easy IL channel. Cable RL peaks above limit of proposed mask.

- High speed TX jitter requirements expected to be in 1ps rms range.

- For crystal-less operation, the CDR has to recover a clean clock from the eye

- Is a simple receiver architecture sufficient for ACT RX ?

# Thank You!

IEEE 802.3dm –July, 2025