2xx Physical Coding Sublayer (PCS), Physical Medium Attachment (PMA) sublayer, and baseband medium, type 2.5G/100MBASE-T1-L, 2.5G/100MBASE-T1-H, 5G/100MBASE-T1-L, 5G/100MBASE-T1-H, 10G/100MBASE-T1-L, 10G/100MBASE-V1-L, 2.5G/100MBASE-V1-L, 2.5G/100MBASE-V1-L, 3G/100MBASE-V1-L, 3G/100MBASE-V1-L, and 10G/100MBASE-V1-H

This is a draft proposal for how a Clause could be structured based on the P802.3dm project documents, including Objectives. This provides flexibility to have different requirements for the different speeds and cabling. Subclauses can be combined later if the requirements are the same, or the requirement can be put in the first subclause in the document and the one later in the document can refer back to it.

Due to the fact that we are limited to a maximum of five levels in the specification, the high speed and low speed requirements are in separate subclauses without a subsection above the pair. This is also the case for the coax and shielded balanced copper cabling.

#### 2xx.1 Overview

May be added by Editor based on project details.

## 2xx.1.1 Nomenclature

May be added by Editor based on project details.

In order to efficiently describe the three PHYs, the nomenclature MultiG is used to abbreviate 2.5G/5G/10G when referring to the set of PHYs.

## 2xx.1.2 PHY/PMD types

I have included a table here to show the different PHYs to be defined and what all the characters that I am using in the names mean. These are subject to approval.

x/y - x is the high transmit speed, y is the low transmit speed

T1 – single shielded balanced pair of conductors (SBP)

V1 – single coaxial cable (Coax)

L – device that transmits at the low speed and receives at the high speed

H – device that transmits at the high speed and receives at the low speed

| PHY name           | Transmit speed | Receive speed | Cable type |

|--------------------|----------------|---------------|------------|

| 2.5G/100MBASE-T1-L | 100M           | 2.5G          | SBP        |

| 2.5G/100MBASE-T1-H | 2.5G           | 100M          | SBP        |

| 5G/100MBASE-T1-L   | 100M           | 5G            | SBP        |

| 5G/100MBASE-T1-H   | 5G             | 100M          | SBP        |

| PHY name           | Transmit speed | Receive speed | Cable type |

|--------------------|----------------|---------------|------------|

| 10G/100MBASE-T1-L  | 100M           | 10G           | SBP        |

| 10G/100MBASE-T1-H  | 10G            | 100M          | SBP        |

| 2.5G/100MBASE-V1-L | 100M           | 2.5G          | Coax       |

| 2.5G/100MBASE-V1-H | 2.5G           | 100M          | Coax       |

| 5G/100MBASE-V1-L   | 100M           | 5G            | Coax       |

| 5G/100MBASE-V1-H   | 5G             | 100M          | Coax       |

| 10G/100MBASE-V1-L  | 100M           | 10G           | Coax       |

| 10G/100MBASE-V1-H  | 10G            | 100M          | Coax       |

# 2xx.1.3 Relationship of MULTIG/100MBASE-T1/V1-L/H to other standards

May be added by Editor based on project details.

## 2xx.1.4 Operation of MULTIG/100MBASE-T1/V1-L/H

Summary provided by contribution later in project

## 2xx.1.4.1 Physical Coding Sublayer (PCS) -H

For the high data rate direction, the MultiG/100M-BASE-T1 PCS couples a 10 Gigabit Media Independent Interface (XGMII), as specified in 46, to the 2.5G/100M-BASE-T1, 5G/100M-BASE-T1, or 10G/100M-BASE-T1 Physical Medium Attachment (PMA) sublayer. In addition to the normal mode of operation, the PCS supports a training mode. Furthermore, the PCS contains a management interface.

In the high data rate direction, the PCS functions as specified in 149.

## 2xx.1.4.2 Physical Coding Sublayer (PCS) -L

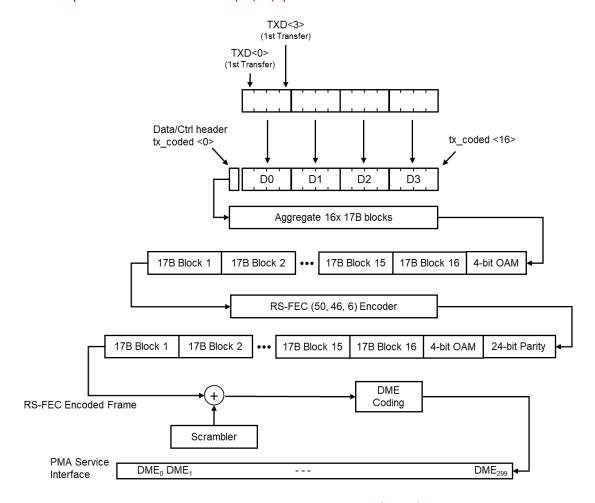

In the low data rate direction, in normal mode, the PCS receives 16 bits MII data provided by four consecutive transfers on the MII service interface on TXD<3:0> and groups them into 16-bit blocks with the 4-bit block boundaries aligned with the boundary of the two MII transfers. Each group of 16-bits along with the data/control indications is transcoded into a 17-bit block. These 17-bit blocks are then aggregated into groups of two blocks. The contents of each group are contained in a vector tx\_group16x17B. Next, a 4-bit OAM field is appended to form a 276-bit block. Each of these 276 bit blocks is formed into an RS-FEC input frame, then encoded by the RS-FEC (50,46,6). The RS-FEC output superframe consists of 300 bits. The duration of the frame is 2560 ns. Finally these bits are exclusive OR'd with a 33-bit self-synchronizing scrambler to create the MultiG/100M-BASE-T1 payload. The low data rate direction PCS transmit functions are described in XXX.3.2.2.

The tx\_group-16x17B <271:0> is defined as:  $tx_group-16x17B <17 \times i + j> = tx_codedi$

where i = 0 to 15, j = 0 to 16, and  $tx\_codedi<16:0>$  is the i-th 16B/17B block where  $tx\_coded0<16:0>$  is the first block transmitted.

In the training mode (see XXX.4.2.4), the PCS transmits and receives DME training frames to synchronize to the PHY frame (and exchanges EEE and MultiG/100M-BASE-T1 OAM capabilities).

Details of the PCS functions and state diagrams are covered in XXX.3. The interface to the PMA is an abstract message-passing interface specified in XXX.4.

### 2xx.1.4.3 Physical Medium Attachment (PMA) sublayer -H

The PMA couples messages from the PCS service interface onto single balanced pair of conductors (T1) or single coaxial cables (V1) via the Medium Dependent Interface (MDI) and provides the link management and PHY Control functions.

The PMA provides asymmetric data rate communications with 5625 x S MBd high speed and 117.1875 MBd low speed. See Table XXX–1 for the definition of S. The PMA PHY Control function generates signals that control the PCS and PMA sublayer operations. PHY Control is enabled following the completion of Auto-Negotiation or PHY Link Synchronization and provides the startup functions required for successful MultiG/100M-BASE-T1 operation. It determines whether the PHY operates in a disabled state, a training state, or a data state where MAC frames can be exchanged between the link partners.

The Link Monitor determines the status of the underlying link channel and communicates this status to other functional blocks. A failure of the receive channel causes the data mode operation to stop and Auto-Negotiation or Link Synchronization to restart.

PMA functions and state diagrams are specified in 2xx.6 and 2xx.7. The electrical parameters of the PMA, i.e., test modes and electrical specifications for the transmitter and receiver, are specified in 2xx.8 and 2xx.9.

The PMA functions for the high data rate direction are as specified in 149.4 with the exceptions in this clause.

### 2xx.1.4.4 Physical Medium Attachment (PMA) sublayer -L

NOTE: It is probably sufficient to have single section for low speed and high speed for this section.

## 2xx.1.4.5 EEE Capability

May want to include and indicate there is no EEE Capability if it is decided this is not needed/required/desired.

## 2xx.1.4.6 Link Synchronization

The Link Synchronization function is used when Auto-Negotiation is disabled or not implemented to detect the presence of the link partner, time and control link failure, and act as the data source for the PHY control state diagram. Link Synchronization operates in a half-duplex fashion. Link Synchronization is defined in <REF>.

## 2xx.1.4.7 Link Synchronization

*NOTE: This section is probably redundant since there should be single section for* low speed *and* high speed.

### 2xx.1.5 Signaling, -H

MultiG/100M-BASE-T1/V1-H signaling is performed by the PCS generating continuous code-group sequences that the PMA transmits over single balanced pair of conductors (T1) or single coaxial cable (V1). The signaling scheme achieves a number of objectives including:

- a) Forward error correction (FEC) coded symbol mapping for data.

- b) Algorithmic mapping from TXD<31:0> and TXC<3:0> to PAM4 symbols in the high speed transmit path.

- c) Algorithmic mapping from the received signal on the MDI port to RXD<31:0> and RXC<3:0>.

- d) Uncorrelated symbols in the transmitted symbol stream.

- e) No correlation between symbol streams traveling both directions.

- f) Block framing and other control signals.

- g) Ability to signal the status of the local receiver to the remote PHY to indicate that the local receiver is not operating reliably and requires retraining.

- h) Ability to automatically detect and correct for incorrect polarity in the connection.

- i) Optionally, ability to support refresh, quiet, and alert signaling during LPI operation.

The PHY may operate in three basic modes: the normal data mode, the training mode, or an optional LPI mode.

In high speed direction, the PCS operates according to Clause 149.

## 2xx.1.6 Signaling, -L

MultiG/100M-BASE-T1/V1-L signaling is performed by the PCS generating continuous code-group sequences that the PMA transmits over single balanced pair of conductors (T1) or single coaxial cable (V1). The signaling scheme achieves a number of objectives including:

- a) Forward error correction (FEC) coded symbol mapping for data.

- b) Algorithmic mapping from TXD<3:0> and TXC<3:0> to DME symbols in the high speed transmit path.

- c) Algorithmic mapping from the received signal on the MDI port to RXD<3:0> and RXC<3:0>.

- d) Uncorrelated symbols in the transmitted symbol stream.

- e) No correlation between symbol streams traveling both directions.

- f) Block framing and other control signals.

- g) Ability to signal the status of the local receiver to the remote PHY to indicate that the local receiver is not operating reliably and requires retraining.

- h) Ability to automatically detect and correct for incorrect polarity in the connection.

- i) Optionally, ability to support refresh, quiet, and alert signaling during LPI operation.

The PHY may operate in two basic modes: the normal data mode or the training mode.

In low speed direction and normal mode, the PCS generates a continuous stream of DME symbols that are transmitted via the PMA. In training mode, the PCS is directed to generate only TBD\_training symbols for transmission by the PMA. (See Figure <REF>

## 2xx.1.7 Interfaces

All MULTIG/100MBASE-T1/V1-L/H PHY implementations are compatible at the MDI and at the MII/XGMII, if implemented. Implementation of the MII and XGMII is optional. Designers are free to implement circuitry within the PCS and PMA in an application-dependent manner provided that the MDI and MII/XGMII (if the MII/XGMII is implemented) specifications are met. System operation from the perspective of signals at the MDI and management objects are identical whether the MII/XGMII is implemented or not. The MDI for single balanced pair of conductors (T1) or single coaxial cable (V1), are different.

### 2xx.1.8 Conventions in this clause

### Standard text

2xx.2 MULTIG/100MBASE-T1/V1-H service primitives and interfaces, high speed channel Service primitives and interfaces the high speed direction are as described in Clause 149.2.

2xx.3 MULTIG/100MBASE-T1/V1-L service primitives and interfaces, low speed channel MultiG/100MBASE-T1/V1-L transfers data and control information across the following four service interfaces:

- a) Media Independent Interface (MII)

- b) Technology Dependent Interface

- c) PMA service interface

- d) Medium Dependent Interface (MDI)

The MII is specified in Clause 22; the Technology Dependent Interface is specified in 98.4. The PMA service interface is defined in <REF> and the MDI is defined in <REF>.

## 2xx.3.1 Technology Dependent Interface

This section is only needed if Auto-Negotiation is supported

2xx.3.1.1 PMA\_LINK.request

2xx.3.1.2 PMA\_LINK.indication

### 2xx.3.2 PMA service interface

MultiG/100MBASE-T1/V1-L service interface is as specified in 149.2.2, with the exceptions given in this subclause.

### 2xx.3.2.1 PMA TXMODE.indication

The transmitter in a MultiG/100MBASE-T1/V1-L link normally sends over the MDI symbols that represent an MII data stream with framing, scrambling and encoding of data, control information, or idles.

NOTE: Update figure 149-3 with MII instead of XGMII.

## 2xx.3.2.2 PMA\_CONFIG.indication

As specified for MultiGBASE-T1 PHYs in 149.2.2.2.

#### 2xx.3.2.3 PMA UNITDATA.request

PMA\_UNITDATA.request(tx\_symb)

During low data rate transmission, the PMA\_UNITDATA.request simultaneously conveys to the PMA via the parameter tx\_symb the value of the symbols to be sent over the MDI. The tx\_symb may take on one of the following values:

- The DME in normal operation.

- 0 when zeros are to be transmitted in the following two cases:

when PMA\_TXMODE.indication is SEND\_Z during PMA training, and

after data mode is reached, the transmit function is in the LPI transmit mode, and lpi\_tx\_mode is QUIET.

### 2xx.3.2.4 PMA\_UNITDATA.indication

The low data rate PMA generates PMA\_UNITDATA.indication(rx\_symb) messages synchronously for every symbol received at the MDI. The nominal rate of the low data rate PMA\_UNITDATA.indication primitive is S\_up x 11250 MHz; as governed by the recovered clock.

2xx.3.2.5 PMA\_SCRSTATUS.request

As specified for MultiGBASE-T1 PHYs in 149.2.2.5.

2xx.3.2.6 PMA\_PCSSTATUS.request

As specified for MultiGBASE-T1 PHYs in 149.2.2.6.

2xx.3.2.7 PMA\_RXSTATUS.indication

As specified for MultiGBASE-T1 PHYs in 149.2.2.7.

2xx.3.2.8 PMA REMRXSTATUS.request

As specified for MultiGBASE-T1 PHYs in 149.2.2.8.

2xx.3.2.9 PMA PCSDATAMODE.indication

As specified for MultiGBASE-T1 PHYs in 149.2.2.9.

2xx.3.2.10 PMA\_PCS\_RX\_LPI\_STATUS.request

If EEE is supported.

2xx.3.2.11 PMA\_PCS\_TX\_LPI\_STATUS.request

*If EEE is supported.*

2xx.3.2.12 PMA ALERTDETECT.indication

If EEE is supported.

2xx.4 Physical Coding Sublayer (PCS) functions,-H

The PCS functions for MultiG/100MBASE-T1/V1-H are as specified for MultiGBASE-T1 PHYs in 149.3.

2xx.5 Physical Coding Sublayer (PCS) functions,-L

## 2xx.5.1 PCS service interface (MII)

The low data rate PCS service interface allows the MultiG/100BASE-T1/V1-L PCS to transfer information to and from a PCS client. The PCS service interface is precisely defined as the Media Independent Interface (MII) in Clause 22.

2xx.5.2 PCS functions

NOTE: Copy of Figure 149-4 needs to be updated to reflect MII instead of XGMII.

2xx.5.2.1 PCS Reset function

The low data rate PCS reset function shall be as specified in Clause 149.3.2.1

### 2xx.5.2.2 PCS Transmit function, -L

The PCS transmit functions for MULTIG/100M-BASE-T1/V1-L for the low data rate direction is described in this sub-clause.

After mapping the 64-MII transfers to 16B/17B blocks, the subsequent functions of the PCS Transmit process take 16 17B blocks and append 4-bit OAM field to each group. This forms the input to the RS-FEC which adds 24 parity bits. The resulting 300 bits are then scrambled.

These bits are then mapped, to DME symbol. Transmit data-units are sent to the PMA service interface via the PMA\_UNITDATA.request primitive. In each symbol period, when communicating with the PMA, the PCS Transmit generates a DME symbol that is transferred to the PMA via the PMA\_UNITDATA.request primitive. The symbol period, T, is  $1000 / (11.250 \times S_up)$  ps. See Table XXX-1 for the definition of  $S_up$ .

The operation of the PCS Transmit function is controlled by the PMA\_TXMODE.indication message received from the PMA PHY Control function. If a PMA\_TXMODE.indication message has the value SEND\_Z, PCS Transmit shall pass a vector of zeros at each symbol period to the PMA via the PMA\_UNITDATA.request primitive.

If a PMA\_TXMODE.indication message has the value SEND\_T, PCS Transmit shall generate a sequence (Tn) defined in 149.3.5.1 to the PMA via the PMA\_UNITDATA.request primitive. These code-groups are used for training mode and only transmit the values #TBD\_training.

During training mode an Infofield is transmitted at regular intervals containing messages for startup operation. By this mechanism, a PHY indicates the status of its own receiver to the link partner and makes requests for remote transmitter settings. (See 149.4.2.4.)

If a PMA\_TXMODE.indication message has the value SEND\_N, the PCS is in the normal mode of operation and the PCS Transmit function shall use a 17B coding technique to generate, at each symbol period, code-groups that represent data or control. During transmission, the 16 blocks of 17B encoded bits are appended with 10-bit OAM field to form the RS-FEC input frame.

During data encoding, PCS Transmit utilizes Reed-Solomon encoders to generate and append 24 parity check bits to form 300 bit RS(50, 46, 6) RS-FEC frames.

Each RS-FEC input frame consists of 276 bits, or 46 Reed-Solomon message symbols. After encoding, the RS-FEC frames from each encoder are recombined into one single interleaved RS-FEC frame, which consists of 50 symbols, or 300 bits. The bits of the RS-FEC frame are then scrambled by the PCS using an additive scrambler, encoded in DME symbols, and transferred to the PMA.

A block diagram of the PCS Transmit functions is shown in Figure 2XX–5.

#### 2xx.5.2.2.1 Use of blocks

The PCS maps MII signals into 17-bit blocks inserted into an RS-FEC frame, and vice versa, using a 17B RS-FEC coding scheme. The PMA training frame synchronization allows establishment of RS-FEC frame and 17B boundaries by the PCS Synchronization process. Blocks and frames are unobservable and have no meaning outside the PCS.

### 2xx.5.2.2.2 17B RS-FEC transmission code

The low speed direction RS-FEC is RS(50,46,6).

Figure 2XX-5 - PCS Transmit bit ordering

### 2xx.5.2.2.3 Notation conventions

For values shown as binary, the leftmost bit is the first transmitted bit.

16B/17B encodes 2 data octets or control characters into a block. Blocks containing control characters also contain a block type field. Data octets are labeled  $D_0$  to  $D_1$ . Control characters other than O/, S/, and T/ are labeled  $C_0$  to  $C_3$ . The control character for ordered set is labeled as  $O_0$  to  $O_3$ . The control character for start is labeled as  $S_0$  to  $S_4$  for the same reason. The control character for terminate is labeled as  $T_0$  to  $T_3$ .

For MultiG/100BASE-T1/V1-L, four MII transfers provide four characters that are encoded into one 17-bit transmission block. The subscript in the above labels indicates the position of the character in the four characters from the MII transfer(s).

## 2xx.5.2.2.4 Block structure

ToDo: add text based on <a href="https://www.ieee802.org/3/dg/public/May-2024/Lo-3dg-01\_1024.pdf">https://www.ieee802.org/3/dg/public/May-2024/Lo-3dg-01\_1024.pdf</a>

```

2xx.5.2.2.5 Control codes

```

2xx.5.2.2.6 Ordered sets

2xx.5.2.2.7 Idle (/I/)

2xx.5.2.2.8 LPI (/LI/)

2xx.5.2.2.9 Start (/S/)

2xx.5.2.2.10 Terminate (/T/)

2xx.5.2.2.11 Ordered set (/O/)

2xx.5.2.2.12 Error (/E/)

2xx.5.2.2.13 Transmit process

## 2xx.5.2.2.14 RS-FEC framing and RS-FEC encoder

The PCS uses a transmission code to improve the transmission characteristics of information to be transferred across the link and to support transmission of control and data characters.

The relationship of block bit positions to MII, PMA, and other PCS constructs is illustrated in Figure 2XX—6 for transmit and Figure 2XX—7 for receive. These figures illustrate the processing of a multiplicity of blocks containing 32 data octets. See 2xx.4.2.2.4 for information on how blocks containing control characters are mapped.

### 2xx.5.2.2.15 Reed-Solomon encoder

The group of 300 bits are encoded using a Reed-Solomon encoder operating over the Galois Field GF(2<sup>6</sup>) where the symbol size is 6 bits. The encoder processes 46 6-bit RS-FEC message symbols to generate 4 6-bit RS-FEC parity symbols, which are then appended to the message to produce a codeword of 50 6-bit RS-FEC symbols. For the purposes of this clause, the particular Reed-Solomon code is denoted as RS-FEC(50,46).

## 2xx.5.2.2.16 PCS scrambler

The bits of the interleaved RS-FEC superframe are scrambled using an additive scrambler. For each bit,  $D_n$ , a scrambler bit is generated from the side-stream scrambler. The scrambler bit,  $DS_n$ , is equal to Scrn[0] defined in 149.3.4.

DSn is applied as additive scrambler sequences to incoming data bits  $D_n$  to generate the scrambled data bit  $A_n$  as shown in Equation (2XX–4).

$$A_n = DS_n \oplus D_n \tag{2xx-4}$$

### 2xx.5.2.2.17 Differential Manchester encoding (DME)

The scrambled data bit, A<sub>n</sub>, is encoded using Differential Manchester Encoding (DME).

## 2xx.5.2.2.18 EEE capability

Only need if supporting EEE

### 2xx.5.2.3 PCS Receive function

The PCS Receive function shall conform to the PCS 16B/17B Receive state diagram in Figure <REF> and Figure <REF>, and the PCS Receive bit ordering in Figure <REF> including compliance with the associated state variables as specified in <REF>.

The PCS Receive function accepts received code-groups provided by the PMA Receive function via the parameter rx\_symb. The PCS receiver uses knowledge of the encoding rules and PMA training alignment to correctly align the 17B RS-FEC frames. The received DME symbols are demapped and descrambling is performed.

Following descrambling, the Reed-Solomon frames are decoded with Reed-Solomon error correction. Frames that cannot be corrected are marked with error symbols by the decoder. The RS-FEC decoded frame is then separated into a 4-bit OAM field and 16 16B/17B blocks. This process generates the 16B/17B block vector rx\_coded<16:0>, which is then decoded to form the MII signals RXD<3:0> and RXC<3:0> as specified in the PCS 16B/17B Receive state diagram (see Figure <REF> and Figure <REF>). Four MII data transfers are decoded from each block. Where the MII and PMA sublayer data rates are not synchronized, the receive process inserts idles, deletes idles, or deletes sequence ordered sets to adapt between rates.

During PMA training mode, PCS Receive checks the received TBD framing and signals the reliable acquisition of the descrambler state by setting the scr\_status parameter of the PMA\_SCRSTATUS.request primitive to OK.

When the PCS Synchronization process has obtained synchronization, the RS-FEC frame error ratio (RFER) monitor process monitors the signal quality and asserts hi\_rfer to indicate excessive RS-FEC frame errors. If 40 consecutive RS-FEC frame errors are detected, the block\_lock flag is de-asserted. The block\_lock flag is re-asserted upon detection of a valid RS-FEC frame. When block\_lock is asserted and hi\_rfer is de-asserted, the PCS Receive process continuously accepts blocks. The PCS Receive process monitors these blocks and generates RXD <3:0> and RXC <3:0> on the MII.

When the receive channel is in training mode, the PCS Synchronization process continuously monitors PMA\_RXSTATUS.indication(loc\_rcvr\_status). When loc\_rcvr\_status indicates OK, then the PCS Synchronization process accepts data-Lnits via the PMA\_UNITDATA.indication primitive. It attains frame and block synchronization based on the PMA training frames and conveys received blocks to the PCS Receive process. The PCS Synchronization process sets the block\_lock flag to indicate whether the PCS has obtained synchronization. The PMA training frame includes an alignment bit every TBD symbols, which is aligned with the PCS partial PHY frame boundary, as well as an Infofield, which is inserted in the

16th PCS partial PHY frame. When the PCS Synchronization process is synchronized to this pattern, block lock is asserted.

## 2xx.5.2.3.1 Frame and block synchronization

When operating in the data mode, the receiving PCS shall form a DME stream from the PMA\_UNITDATA.indication primitive by concatenating requests in order from rx\_DME\_0 to rx\_DME\_299 (see Figure <REF>). It obtains block lock to the PHY frames during training using synchronization bits provided in the training frames.

### 2xx.5.2.3.2 PCS descrambler

The descrambler processes the payload to reverse the effect of the scrambler using the same polynomial. The PCS descrambles the data stream and returns the proper sequence of symbols to the decoding process for generation of RXD<3:0> to the MII. For side-stream descrambling, the MASTER PHY shall employ the receiver descrambler generator polynomial per Equation (149–6) and the SLAVE PHY shall employ the receiver descrambler generator polynomial per Equation (149–5).

### 2xx.5.2.3.3 Invalid blocks

A block is invalid if any of the following conditions exist:

- a) The block type field contains a reserved value.

- b) Any control character contains a value not in Table <REF>.

- c) Any O code contains a value not in Table <REF>.

- d) The block contains information from the payload of an invalid RS-FEC frame.

The PCS Receive function shall check the integrity of the RS-FEC parity bits defined in <REF>. If the check fails the RS-FEC frame is invalid.

The R\_BLOCK\_TYPE of an invalid block is set to E.

## 2xx.5.3 Test-pattern generators

For MultiG/100BASE-T1/V1-L test-pattern generator follows Clause 149.3.3, with the exception that the transmission follows illustration in Figure <REF> instead or Figure 149-6 and Figure <REF> instead of Figure 149-7.

### 2xx.5.4 Side-stream scrambler polynomials

For MultiG/100BASE-T1/V1-L side-stream scrambler is as specified in 149.3.4.

### 2xx.5.5 PMA training frame

The MultiG/100BASE-T1/V1-L training frame is TBD.

## 2xx.5.5.1 Generation of symbol $T_n$

The MultiG/100BASE-T1/V1-L T<sub>n</sub> symbol is TBD.

## 2xx.5.5.2 PMA training mode descrambler polynomials

The MultiG/100BASE-T1/V1-L training mode descrambler is TBD.

### 2xx.5.6 LPI signaling

Only need if supporting EEE

2xx.5.7 Detailed functions and state diagrams

2xx.5.7.1 State diagram parameters

2xx.5.7.1.1 Constants

2xx.5.7.1.2 Variables

2xx.5.8 PCS management

2xx.5.9 MULTIG/100MBASE-T1/V1-L operations, administration, and maintenance (OAM) *Only if OAM is used in low speed direction.*

## 2xx.6 Physical Medium Attachment (PMA) sublayer, -H

I did not include all subclauses as they can vary with implementation. You can look at any PHY project that is similar to see which may be needed. Other subclauses may be added as baselines are chosen.

The high speed PMA functions are as specified in 149.4.

## 2xx.7 Physical Medium Attachment (PMA) sublayer, -L

I did not include all subclauses as they can vary with implementation. You can look at any PHY project that is similar to see which may be needed. Other subclauses may be added as baselines are chosen.

The low speed PMA Transmit function comprises a transmitter to generate a DME signal on the MDI interface.

2xx.7.1 PMA functional specifications

## 2xx.7.2 PMA functions

The PMA sublayer comprises one PMA Reset function and five simultaneous and asynchronous operating functions. The PMA operating functions are PHY Control, PMA Transmit, PMA Receive, Link Monitor, and Clock Recovery. All operating functions are started immediately after the successful completion of the PMA Reset function.

The PMA reference diagram, Figure <REF>, shows how the operating functions relate to the messages of the PMA service interface and the signals of the MDI. Connections from the management interface, comprising the signals MDC and MDIO, to other layers are pervasive and are not shown in Figure <REF>.

### 2xx.7.2.1 PMA Reset function

The PMA Reset function shall be executed whenever one of the two following conditions occur:

- a) Power for the device containing the PMA has not reached the operating state.

- b) The receipt of a request for reset from the management entity.

PMA Reset sets pma\_reset = ON while any of the above reset conditions hold TRUE. All state diagrams take the open-ended pma\_reset branch upon execution of PMA Reset. The reference diagrams do not explicitly show the PMA Reset function.

The MultiG/100MBASE-T1/V1-L PMA takes no longer than TBD ms to enter the PCS\_DATA state after exiting from reset or low power mode (see Figure 149–32).

#### 2xx.7.2.2 PMA Transmit

The PMA Transmit function comprises a transmitter to generate a DME modulated signal on the single balanced pair of conductors (T1) or Coaxial cable (V1). When the PHY Control state diagram (Figure 149–32) is not in the DISABLE\_TRANSMITTER state, PMA Transmit shall continuously transmit pulses modulated by the symbols given by tx\_symb onto the MDI. During Link Synchronization, when sync\_link\_control = DISABLE and Auto-Negotiation is either not enabled or is not implemented, the sync\_tx\_symb output by the PHY Link Synchronization function shall be used in place of tx\_symb as the data source for PMA Transmit. The signals generated by PMA Transmit shall comply with the electrical specifications given in 149.5.2.

When the PMA\_CONFIG.indication parameter config is MASTER, the PMA Transmit function shall source TX\_TCLK from a local clock source while meeting the transmit jitter requirements of 149.5.2.3. The MASTER-SLAVE relationship shall include loop timing. If the PMA\_CONFIG.indication parameter config is SLAVE, the PMA Transmit function shall source TX\_TCLK from the recovered clock of 149.4.2.8 while meeting the jitter requirements of TBD.

The PMA Transmit fault function is optional. The faults detected by this function are implementation specific. If the MDIO interface is implemented, then this function shall be mapped to the transmit fault bit as specified in 45.2.1.7.4.

When the PMA\_transmit\_disable variable is set to TRUE, this function shall turn off the transmitter so that the average launch power of the transmitter is less than –53 dBm.

### 2xx.7.2.4 PMA Receive function

The low speed PMA Receive function comprises a receiver for DME signal on the MDI. PMA Receive contains the circuits necessary to both detect symbol sequences from the signals received at the MDI and to present these sequences to the PCS Receive function. The PMA translates the signals received at the MDI into the PMA\_UNITDATA.indication parameter rx\_symb. The quality of these symbols shall allow RFER of less than 2 x after RS-FEC decoding, over a channel meeting the requirements of 149.7.

The low speed direction PMA Receiver function uses the parameters pcs\_status and scr\_status, along with other applicable receiver status, and generates the loc\_rcvr\_status variable accordingly The loc\_rcvr\_status variable is expected to become NOT\_OK when the link partner's tx\_mode changes to SEND\_Z from any other value (see the PHY Control state diagram in Figure 149–32). The precise algorithm for generation of loc\_rcvr\_status is implementation dependent.

The receiver uses the sequence of symbols during the training sequence to detect and correct for pair polarity swaps.

The PMA Receive fault function is optional. The PMA Receive fault function is the logical OR of the link\_status = FAIL and any implementation specific fault. If the MDIO interface is implemented, then this function shall contribute to the receive fault bit specified in 45.2.1.7.5 and 45.2.1.193.7.

### 2xx.7.2.6 PHY Control function

The MultiG/100MBASE-T1/V1-L PHY control functions are as specified in 149.4.2.4.

### 2xx.7.2.8 Link Monitor function

The MultiG/100MBASE-T1/V1-L link monitoring functions are as specified in 149.4.2.5.

## 2xx.7.2.9 PHY Link Synchronization

The MultiG/100MBASE-T1/V1 link synchronization is TBD.

## 2xx.7.2.10 Refresh monitor function

Only needed if EEE is implemented.

## 2xx.7.2.11 Clock Recovery function

The Clock Recovery function shall provide a clock suitable for signal sampling so that the RFER indicated in 2xx.7.2.4 is achieved. The received clock signal is expected to be stable and ready for use when training has been completed. The received clock signal is supplied to the PMA Transmit function by received\_clock.

## 2xx.7.3 MDI, T1

The MDI signals are as specified in 149.4.3, with the exception that low speed signaling uses DME instead of PAM4.

### 2xx.7.4 MDI, V1

The MDI signals are as specified in 149.4.3, with the exception that low speed signaling uses DME instead of PAM4, and that the signals are single ended instead of differential.

#### 2xx.7.5 State variables

The MultiG/100MBASE-T1/V1-L state variables are as specified in 149.4.4.

## 2xx.7.6 State diagrams

The MultiG/100MBASE-T1/V1-L state diagrams are as specified in 149.4.4.

## 2xx.8 Physical Medium Dependent (PMD) sublayer, T1

This subclause defines the electrical characteristics of the PMA and specifies PMA-to-MDI interface tests, for differential balanced pair (T1).

### 2xx.8.1 Test modes

The MultiG/100MBASE-T1-H/L test modes, including the test fixtures, are as specified in 149.5.1.

## 2xx.8.2 Transmitter electrical specifications

The MultiG/100MBASE-T1-H/L transmitter electrical specifications are as specified in 149.5.2, with the exceptions listed in this sub-clause.

### 2xx.8.2.1 Maximum output droop

As specified for MultiGBASE-T1 PHYs in 149.5.2.1.

### 2xx.8.2.2 Transmitter linearity

As specified for MultiGBASE-T1 PHYs in 149.5.2.2.

## 2xx.8.2.3 Transmitter timing jitter

As specified for MultiGBASE-T1 PHYs in 149.5.2.3.

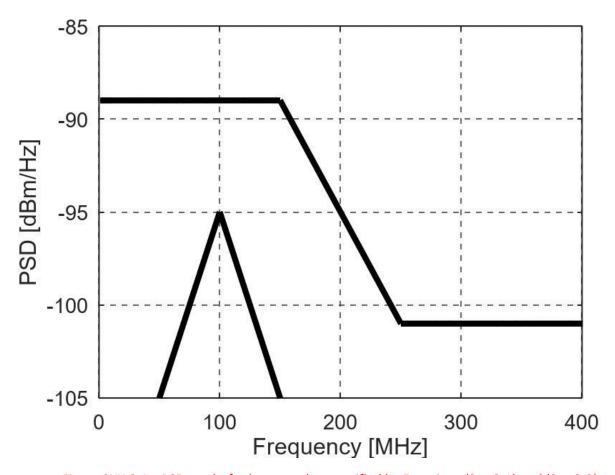

### 2xx.8.2.4 Transmitter power spectral density (PSD) and power level

The MultiG/100MBASE-T1-H transmitter power spectral density (PSD) and power level are as specified in 149.5.2.4.

The MultiG/100MBASE-T1-L transmitter power spectral density (PSD) when measured using test mode 3 and the test fixture shown in Figure 147–16, or equivalent, the transmitter Power Spectral Density (PSD) shall be between the upper and lower masks specified in Equation (2xx.8–1) and Equation (2xx.8–2).

$$UpperPSD(f) = \begin{cases} -58 & 3 \le f < 150 \\ -37 - 1.4f & 150 \le f < 250 \\ -72 & 250 \le f < 400 \end{cases} dBm/Hz \quad (2xx.8-1)$$

and

LowerPSD(f) =

$$\begin{cases} -84 + 2f & 50 \le f < 100 \\ -44 - 2f & 100 \le f < 150 \end{cases} dBm/Hz$$

(2xx.8-2)

where f is the frequency in MHz.

Figure 2XX.9-1—PSD masks for low speed as specified by Equations (2xx.8-1) and (2xx.8-2)

## 2xx.8.2.5 Transmitter peak differential output

As specified for MultiGBASE-T1 PHYs in 149.5.2.5.

### 2xx.8.2.6 Transmitter clock frequency

As specified for MultiGBASE-T1 PHYs in 149.5.2.6.

## 2xx.8.3 Receiver electrical specifications

The MultiG/100MBASE-T1-H/L Receiver electrical specifications are as specified in 149.5.3, with the exception listed in this sub-clause.

The cabling used is according to Clause 2xx.11, instead of Clause 149.7.

## 2xx.8.3.1 Receiver differential input signals

Differential signals received at the MDI that were transmitted from a remote transmitter within the specifications of 2xx.8.2 and have passed through a link specified in 2xx.11 shall be received with a BER less than 10-12 after RS-FEC decoding, and sent to the XGMII/MII after link reset completion. This specification can be verified by a frame error ratio less than  $7.8 \times 10-9$  for 800 octet frames with minimum IPG or greater than 220-octet IPG.

## 2xx.8.3.2 External noise rejection

As specified for MultiGBASE-T1 PHYs in 149.5.3.2.

2xx.8.4 MDI

2xx.8.4.1 MDI signals transmitted by the PHY

2xx.8.4.3 Signals received at the MDI

2xx.9 Physical Medium Dependent (PMD) sublayer, V1

This subclause defines the electrical characteristics of the PMA and specifies PMA-to-MDI interface tests, for coaxial cables (V1).

2xx.9.1 Test modes

2xx.9.1.1 Test fixtures

2xx.9.2 Transmitter electrical specifications

2xx.9.2.1 Maximum output droop

2xx.9.2.2 Transmitter linearity

2xx.9.2.3 Transmitter timing jitter

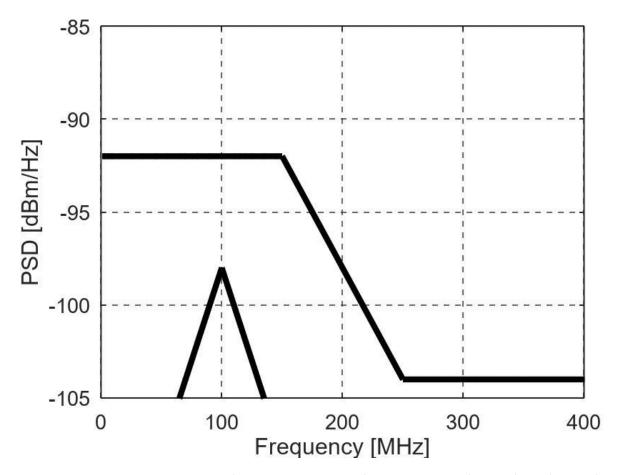

## 2xx.9.2.4 Transmitter power spectral density (PSD) and power level

When measured using test mode 3 and the test fixture shown in Figure <REF>, or equivalent, the transmitter Power Spectral Density (PSD) shall be between the upper and lower masks specified in Equation (2xx.9–1) and Equation (2xx.9–2).

$$UpperPSD(f) = \begin{cases} -61 & 3 \le f < 150 \\ -40 - 1.4f & 150 \le f < 250 \\ -75 & 250 \le f < 400 \end{cases} dBm/Hz \quad (2xx.9-1)$$

and

LowerPSD(f) =

$$\begin{cases} -87 + 2f & 50 \le f < 100 \\ -47 - 2f & 100 \le f < 150 \end{cases} dBm/Hz$$

(2xx.9-2)

where f is the frequency in MHz.

Figure 2XX.9-1—PSD masks for low speed as specified by Equations (2xx.9-1) and (2xx.9-2)

2xx.9.2.5 Transmitter peak output

2xx.9.2.6 Transmitter clock frequency

2xx.9.3 Receiver electrical specifications

2xx.9.3.1 Receiver input signals

2xx.9.3.2 External noise rejection

### 2xx.9.4 MDI

### 2xx.9.4.1 MDI return loss

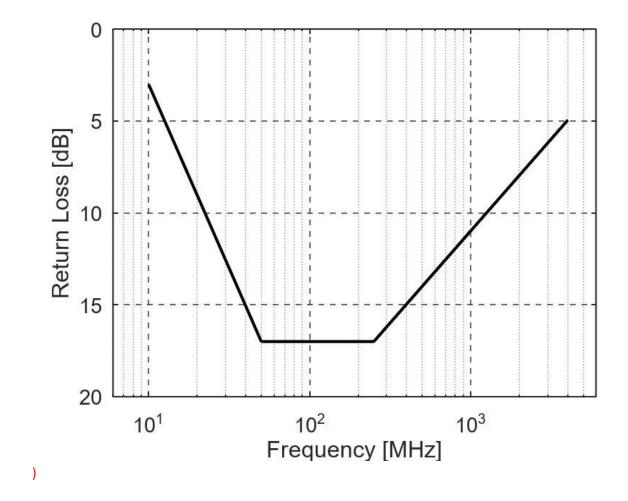

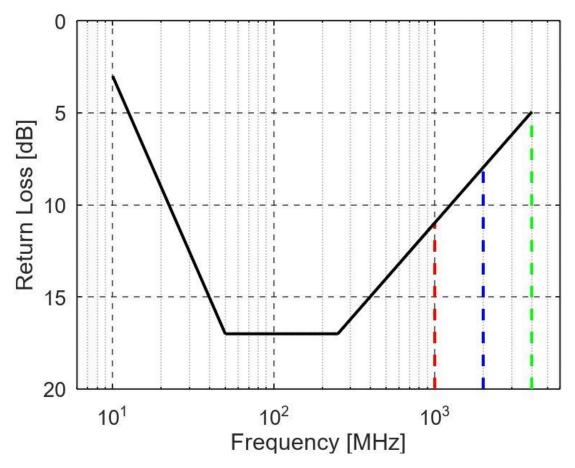

The differential impedance at the MDI for each transmit/receive channel shall be such that any reflection due to signals incident upon the MDI from the cabling relative to the incident signal are per the relationship shown in Equation (2XX.8-1). For coaxial cabling a nominal characteristic impedance of  $50\Omega$  is used.

$$MDI\_Return\_Loss(f) > TBD$$

(2xx.7-1) where  $f$  is the frequency in MHz.

For MULTIG/100MBASE-V1 the maximum applicable frequency,  $F_{max}$ , for the MDI return loss is 1000MHz, 2000MHz, and 4000MHz, respectively.

The MDI return loss for 10G/100MBASE-T1 is illustrated in Figure 2XX.9-2.

Figure 2XX.9-2—MDI return loss calculated using Equation (2XX.8-1)

| 2xx.9.4.1 MDI signals transmitted by the PHY                                |

|-----------------------------------------------------------------------------|

| 2xx.9.4.3 Signals received at the MDI                                       |

| 2xx.10 Management interface                                                 |

| 2xx.11 Link segment characteristics, T1                                     |

| 2xx.11.1 Link transmission parameters                                       |

| 2xx.11.1.1 Insertion loss                                                   |

| 2xx.11.1.2 Differential characteristic impedance                            |

| 2xx.11.1.3 Return loss                                                      |

| 2xx.11.1.4 Coupling attenuation                                             |

| 2xx.11.1.5 Screening attenuation                                            |

| 2xx.11.1.6 Maximum link delay                                               |

| 2xx.11.2 Coupling parameters between link segments                          |

| 2xx.11.2.1 Power sum alien near-end crosstalk (PSANEXT)                     |

| 2xx.11.2.2 Power sum alien attenuation to crosstalk ratio far-end (PSAACRF) |

| 2xx.12 Link segment characteristics, V1                                     |

| 2xx.12.1 Link transmission parameters                                       |

| 2xx.12.1.1 Insertion loss                                                   |

| 2xx.12.1.2 Differential characteristic impedance                            |

| 2xx.12.1.3 Return loss                                                                                                                                        |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2xx.12.1.4 Coupling attenuation                                                                                                                               |

| 2xx.12.1.5 Screening attenuation                                                                                                                              |

| 2xx.12.1.6 Maximum link delay                                                                                                                                 |

| 2xx.12.2 Coupling parameters between link segments  I wasn't sure what the correct parameters are, so I just copied the T1 crosstalk titles for placeholders. |

| 2xx.12.2.1 Power sum alien near-end crosstalk (PSANEXT)                                                                                                       |

| 2xx.12.2.2 Power sum alien attenuation to crosstalk ratio far-end (PSAACRF)                                                                                   |

| 2xx.13 MDI specification, T1                                                                                                                                  |

| 2xx.13.1 MDI connectors                                                                                                                                       |

| 2xx.13.2 MDI electrical specification                                                                                                                         |

| 2xx.13.2.1 MDI return loss                                                                                                                                    |

| 2xx.13.3 MDI fault tolerance                                                                                                                                  |

| 2xx.14 MDI specification, V1                                                                                                                                  |

| 2xx.14.1 MDI connectors                                                                                                                                       |

| 2xx.14.2 MDI electrical specification                                                                                                                         |

| 2xx.14.2.1 MDI return loss                                                                                                                                    |

2xx.14.3 MDI fault tolerance

## 2xx.15 Environmental specifications

The environmental specifications for MULTIG/100M-BASE-T1/V1 are as specified in 149.9.

2xx.15.1 General safety

2xx.15.2 Network safety

2xx.15.2.1 Environmental safety

2xx.15.2.2 Electromagnetic compatibility

## 2xx.16 Delay constraints

The delay constraints for MULTIG/100M-BASE-T1/V1 are as specified in 149.10 with the exceptions and extensions in this sub-clause.

The delay limits for 100Mb/s low speed direction is TBD.

2xx.17 Protocol implementation conformance statement (PICS) proforma for Clause 2xx