Hi Wei,

Thank you once again for your prompt response.

As you can probably tell, I am reading through the New-TDD baseline text in detail, but I was still not sure about the timing relationship between Master and Slave. Thank you for clarifying this relationship.

Regarding the definition of the loc_rcvr_status, I found several statements about loc_rcvr_status:

- According to Clause 200.2.2.7 of New-TDD baseline text, “The criteria for setting the parameter loc_rcvr_(n)_status is left to the implementer.” I assume

that loc_rcvr_(n)_status is same as loc_rcvr_status0, for n=0.

- According to Clause 200.4.2.3 of the New-TDD baseline text, “When loc_rcvr_status indicates OK, then the PCS Synchronization

process accepts data-units via the PMA_UNITDATA.indication primitive.” I understood this to mean that the PCS Synchronization process will only start after loc_rcvr_status is OK.

- According to Clause 200.6.2.3 of the New-TDD baseline text, “The PMA Receive function uses the parameters pcs_status and scr_status, and the state of

the equalization, and estimation functions to determine the quality of the receiver performance, and generates the loc_rcvr_status variable accordingly.” I understand this to mean that that frame synchronization may be required before loc_rcvr_status becomes

OK.

- According to Clause 200.6.4.1 of the New-TDD baseline text, the loc_rcvr_status variable indicates “correct or incorrect operation of the receive link

for the local PHY at the current TRAINING stage.” This suggests to me that there may be more than one valid criterion for setting loc_rcvr_status to OK.

The c-variant above is the same as in 802.3ch, but b-variant may be conflicting with the c-variant. This is why I was not sure how to interpretate loc_rcvr_state set to OK. You have now clarified this for

me.

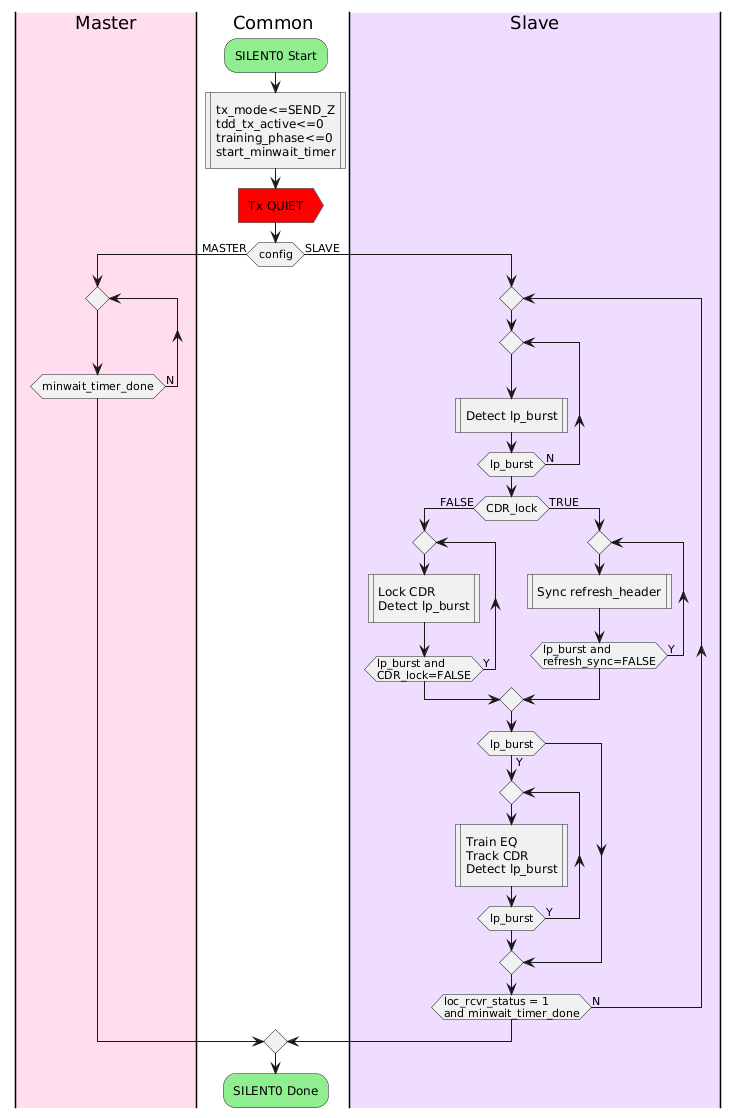

I have created the action diagram below for the SILENT0 state (the second state) in the state diagram in Figure 200-32 in the New-TDD baseline text. Do you think that I am representing correctly what is expected

to happen in the Master and Slave PHYs in the SILENT0 phase?

Ragnar

From: Wei Lou <000047a3c8c56bbe-dmarc-request@xxxxxxxxxxxxxxxxx>

Sent: Thursday, July 10, 2025 9:08 AM

To: STDS-802-3-ISAAC@xxxxxxxxxxxxxxxxx

Subject: Re: [802.3_ISAAC] [EXTERNAL] Re: [802.3_ISAAC] Question on Baseline Text Proposal for TDD Based 802.3dm PHY

Hi, Ragnar, Generally, to address the questions you raised, please refer to TDD proposal's PHY control state diagram which specifies that loc_rcvr_status0= OK is

the condition for SLAVE to change from SILENT0 to TRAINING0. loc_rcvr_status=OK

ZjQcmQRYFpfptBannerStart

|

ZjQcmQRYFpfptBannerEnd

Hi, Ragnar,

Generally, to address the questions you raised, please refer to TDD proposal's PHY control state diagram which specifies that loc_rcvr_status0= OK is the condition for SLAVE to change from SILENT0 to TRAINING0. loc_rcvr_status=OK means " The PMA Receive function uses the parameters pcs_status and scr_status, and the state of the

equalization, and estimation functions to determine the quality of the receiver performance, and generates the loc_rcvr_status variable accordingly." (Section 200.6.2.3)

Based on this definition, the timing_lock= OK is implied when loc_rcvr_status=OK. Other criteria include sufficient SNR margin, etc.

The MASTER will not adjust its transmit clock frequency during the entire training/data mode. It sends out fixed periodic TDD pattern during each Training phase. It will adjust its TDD QUIET/burst duration from Symmetric training to Asymmetric training. SLAVE is responsible to synchronize to MASTER clock.

Wei

________________________________________________________________________

To unsubscribe from the STDS-802-3-ISAAC list, click the following link: https://urldefense.proofpoint.com/v2/url?u=https-3A__listserv.ieee.org_cgi-2Dbin_wa-3FSUBED1-3DSTDS-2D802-2D3-2DISAAC-26A-3D1&d=DwIFaQ&c=nKjWec2b6R0mOyPaz7xtfQ&r=hiHgBSUj2X0k3TORVxe0NCZAlJs6SEDHhwLDz5m9MbY&m=B_1KglipEyOCpIf7GSjT7ypBxf5ADaLCIOOLxFv7GsmIc6OH7M8neKwSM2jlDBys&s=HTL8pSqTJK9DJXM5A5Cq5RMR6Ful6Ghtqd1fv045wjs&e=

To unsubscribe from the STDS-802-3-ISAAC list, click the following link: https://listserv.ieee.org/cgi-bin/wa?SUBED1=STDS-802-3-ISAAC&A=1